SIXTH EDITION

# Computer Organization

## Architecture DESIGNING FOR PERFORMANCE

**William Stallings**

## Computer Organization &Architecture

DESIGNING FOR PERFORMANCE

Www.illiam Stallings' book provides comprehensive and completely up-to-date coverage of computer organization and architecture including memory. VC], and parallel systems. The text covers leading-edge areas, including superscalar design, IA-54 design features, and parallel processor organization trends. It meets students' needs by addressing both the fundamental principles as well as the critical role of performance in driving computer design. Providing an unparalleled degree of instructor and student support, including supplements **and online** resources through the book's website, the sixth edition is in the forefront in its field.

#### NEW

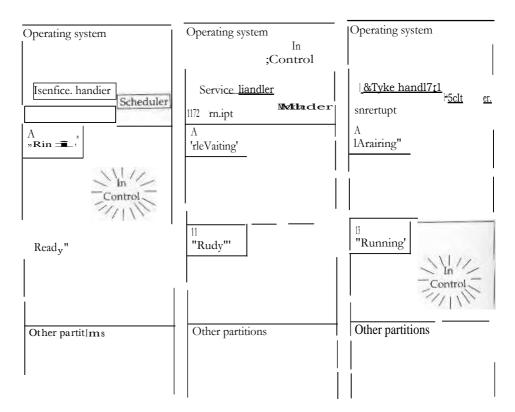

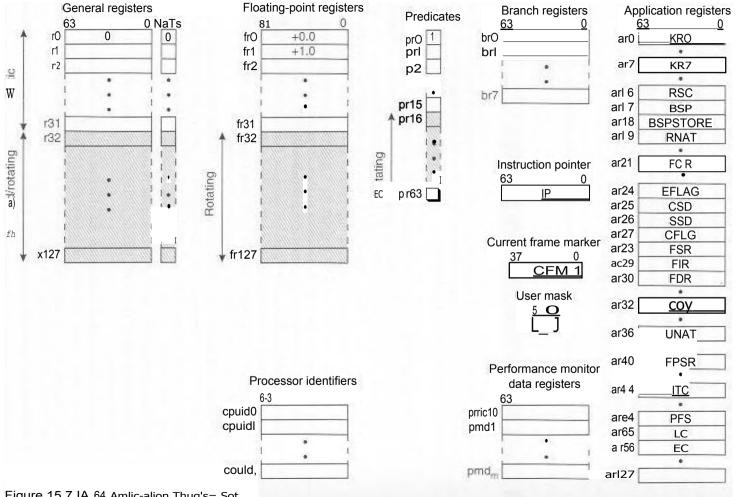

- IA-64/Itanium architecture: chapter-length description and analysis that includes predicated execution and speculative loading.

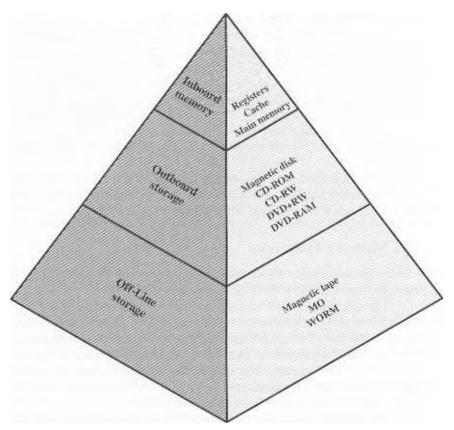

- Cache memory: Cache memory is a central element in the design of high-performance processors. An entire chapter is devoted to this issue in the new edition.

- Optical memory: expanded and updated.

- Advanced DRAM architecture; more material has been added to cover this topic, including an updated discussion of SDRAM and RDRAM,

- SMP's, dusters, and 141)MA systems; the chapter on parallel organization has been expanded and updated.

- Expanded instructor support: the book now provides extensive support for projects with its new website,

- \***Pedagogy:** each chapter now includes **a** list of review questions (as well as homework problems) **and a** list of key words.

#### DISTINGUISHING KEY FEATURES

- Running examples; numerous concrete examples, especially Pentium 4 and Power PC G4.

- Bus organization; detailed treatment and evaluation of key design issues.

- RISC broad, unified presentation-

- \* Microprogrammed implementation: lull treatment for a firm grasp.

- **I/O functions and structures:** provides full understanding and shows interaction of I/O modules with the outside world and the CPU.

- Unified **instructional approach**: enables student to evaluate instruction set design issues.

- Instructors Resource CD-ROM: includes solutions to homework problems, list of research project-S, list of simulation projects **plus student manual for both** SimpleScalar and SMPCache, and a list of suggested reading assignments.

#### THE AUTHOR'S WEBSITE:

http://www.WilliamStallings.comiCOA6e provides support for students, instructors and professionals:

- Links to important up-to-date site-related text materials.

- Provides transparency masters of figures and tables from the book in PDF format.

- Lists a set of course notes in PDP for handouts.

- Includes a set of PowerPoint slides for lecturing,

Prentice Hall Upper Saddle River New Jersey 07458 wwwpreriKall.com

These are unabridged paperback reprints of established titles widely used by universities and colleges throughout the world. Pearson Education International publishes these lower-priced editions for the benefit of students. This edition rnay be sold only in the e countries to which it is consigned by Pearson Education International. It is not to be re-exported, and is not for sale **in the U.S.A., Mexico, or Canada.**

## **Prentice Hall International Editions**

ISDN 0-13-04931:17- 4 9 0 0 0 0 9 780 1 30 49307 1

### THE WILLIAM STALLINGS BOOKS ON COMPUTE !?

### data and computer communications, sixth lannoN

A comprehensive survey that has become the standard in the field. covering (I) data communications, including transmission, media, signal encoding, link control, and multiplexing; (2) communication nchvorks. including circuit- and packet-switched, frame relay, ATM. and LANs: (3) the TCP/IP protocol suite. including IPv6, TCP. M1MF., and HTTP: as well as a detailed treatment of network security. **Received the 21111) Text and Academic Authors Association (TAA) award for tong**-term excellence in a Computer Science Textbook. ISBN 0.13-084370-9

#### **CRYPTOGRAPHY AND NETWORK SECURITY, SECOND EDITION**

A tutorial and survey on network security technology. Each of the basic building blocks of network security, including conventional and public-key cryptography, authentication, and digital signatures, are covered. The book covers important network security tools and applications, including S/MIME. IP Security, Kerberos, SSUMS. SET, and Vil19v3, In addition, methods for countering hackers and viruses are explored. **Received the TAA award for the best Computer Science and Engineering Textbook of 1999.** ISBN 0-13 4;69017-0

#### **OPERATING SYSTEMS, FOURTH EDITION**

A state-of-the art survey of operating system principles. Covers fundamental technology as well as contemporary design issues, such as threads, microkernels, SIVIPs, real-time systems, multiprocessor scheduling, distributed systems, clusters, security, and object-oriented design. **Third edition received the TAA award for the best Computer Science and Engineering Textbook of 1998.** ISBN 0-13-03199q41

#### HIGI I-SPEED NETWORKS AND INTERNETS, SECOND EDITION

A state-of-the art survey of high-speed networks, Topics covered include 'MP congestion control. ATM traffic management, internel traffic management. differentiated and integrated services, interne( routing protocols and multicast routing protocols, resource reservation and RSVP, and lossless and bossy compression. Examines important topic of self-similar data traffic. ISBN 0-13413221-0

### AND DATA COMMUNICATIONS TECHNOLOGY

#### WIRELESS COMMUNICATIONS AND NETWORKS

A comprehensive, slate-of-the art survey. Covers fundamental wireless communications topics, including antennas Lind propagation. signal encoding techniques, spread spectrum, and error correction techniques. Examines satellite, cellular, wireless local loop networks and wireless LANs, including Biuetooth and 144.12.1L Covers Mobile IP and 'NAP. ISBN 0-13-1:W864-6

#### LOCAL AND METROPOLITAN AREA NETWORKS, SIXTH EDITION

An in-depth presentation of I he technology and architecture or local and metropolitan area network, Covers topology, transinksion media, medium access control, standards, internctworking. Vinci notwork management. Provides an up-to-date coverage of LAN•MAN systems, including I.ast Ethernet. Fibre Channel, and wireless LANs, plus LAN QoS. **Received the 2001 TAA award tor long-term excellence in a Computer Science Texthimk.** ISBN 0-i:1-012939-9

#### ISDN AND BROADBAND ISDN, WITH FRAME RELAY AND ATM: FOURTH EDITION

An in-depth presentation of the technology and architecture of integrated services digital networks (ISDN). Covers the integrated digital network (I I)N), x.DSL, ISDN services and architecture. and signaling system no. 7 (SST) and provides detailed coverage of the Ill!-'1' protocol standards. Also provides detailed coverage of protocols **and** congestion control strategies for both frame relay and ATM. ISBN 0;13-973744-5

#### **BUSINESS DATA COMMUNICATIONS, FOURTH EDITION**

A comprehensive presentation of data communications and telecommunication from a business, perspective. Covers voice, data. image, and video communications and applications technology and includes a number of case studies. ISBN 0-1:;-088263-1

#### **NETWORK SECURITY ESSENTIALS**

A lulorial and survey on network security technology. The book covers important network security tools and applications, including WIMP, IP Security. Kerberos. SSL1TLS, SET, and X509v3. In addition, methods for countering hackers and viruses are explored. ISBN t1-13-016093-8

## COMPUTER ORGANIZATION AND ARCHITECTURE

Designing fin' Performance

SIXTH EDITION

William Stallings

Pearson Education International

| Th | ,1411.1100 Ttiny I | ld ad rill if III 11 10,::: LX1L111114::* to which | 1, C.:111!%1F.(1.Ak hy |

|----|--------------------|----------------------------------------------------|------------------------|

| EI | IS M 1 11          | ;11111 II is 17111 firAli. in I ho                 | .{11;{),               |

-kiwnti.11) lintoTriA II{ ом I,

| Vice I <sup>3</sup> feuidciIt and Ed | itorial Director. EC'S: !We      | eida .1. I f orton                       |

|--------------------------------------|----------------------------------|------------------------------------------|

| k'tthli{li r: •1?4+0 X. Ape          |                                  |                                          |

| Managa: d'ecke                       | erreir                           |                                          |

| Ass[}Ui:Ue r                         | 1.5. fledor                      |                                          |

| P.cli1031.11 Ass.iistanr:            |                                  |                                          |

| Vice ['resident alud I.nr            | cci{rr 01 PT4FaLtr. 111111 4trid | ManufacturingfESM: Derthic W. Ric:eon/4' |

| Executive Managing I                 | Editor: Vim O'Brien              |                                          |

| Ariristant Ma nafzing. Ed            | lite Ginn:21f. Tr p.macovw       | ,                                        |

| PrOdiJeCiinl. Edilut: ROM            | A' KPreleet?                     |                                          |

| Dif OCLCIr {)[ Cr eati'vo Se         | ervices: Parr! nelfarret         |                                          |

| C:reative DifeCLOr: Curr             | <b>)h.</b> Arisen                |                                          |

| An Director: firithee CeirLy         | /n'emeii                         |                                          |

| At Editor; Greg Dudes                |                                  |                                          |

| Coyer Designer: firohti.             |                                  | •                                        |

| Manutieci uring                      | Ttud y Pi.xciotti                | 7 224 8                                  |

| Mienurael wring Huiyer:              | bokveU                           |                                          |

| Senior Mu rk MOIII                   | NgC17 <i>iorteie</i>             | €?A                                      |

|                                      |                                  | C. 642.sTri                              |

|                                      |                                  | 0.042.3111                               |

|                                      | Pearson Education, Enc.          | 2003                                     |

| IIV VI Sado                          | dle River. New .Teirsq 1 17      | 15ff <b></b>                             |

All right reser...ell. Nei pan c.).1 this hawk may be reprelalLiCefl, lorr without permission in Writing; 11151/05 the publisher.

lorm or Fry :illy 11':ens.,

The LoLhof and pfiblis her of this hoc 5k have useit their best efforis in preparing this hoc 5k. '1<sup>9</sup>h12S12 **1217**urk include the development. **fesuaieil, arid** I eriaing tof the thee rrit'S. and pre igra m s 1.4<sup>e</sup> determine Muir einem **ive** ness.. The fi utile ir and publisher makeato wa rfart ? cif am kind. expressed or implied, with repard in these prop uins or the documental <sup>131</sup>J111 i cd rn (.his book. he autifor.and rlilh LISh12T Sh I] DAt he liahl.12 If y Yu:L1[ lot incidental L31 LUISS11.11.10hE **iHrnOPc**<sup>4</sup> iii cdn ncction with, ine 7rising uul of, the furnishing. performance, or use. of /hove pi ciAra ms.

Prfniied in thy: /Jailed States cll America

10 7 6' 5 4 3. 2 I

#### ISBN I-13-17149307-4

PiYarSull EdLicition rcarson Education Australia PIN. Lirniied Pearson Education Siiwapore. Pte. Lad. }'Carson Educalroii North Asia Da Peiirsein Eclucaiinr Cat cla. Inc. Pearson Ed ticaiefo n de Mexico, S.A. de C..V. Yen rsem Pdilealion—,11;ipfin Penrson Fclucatinn Malaysia, Pie. Ltd. armin Eclucalion, tipiwiNewirdif. Nod! Lice,p..,tiy As cilways For A. T. S.

## WEB SITE FOR COMPUTER ORGANIZATION AND ARCHITECTURE Sixth Edition

The Web site at WilliamStallings.conA:0A6c.htral provides support for instructors and SALAtTILS using the book. It includes the elernunVi-

## **Course Support Materials**

The course support materials include

- Copies of figures from the book in PDF forma L

- Copies of tables from thu book in PDF format

- A set of PowerPoint slides for use as lecture aids

- A set of PDF course noit; s suitable for student handout or for use 4LS viewgrLiphs

- Computer Science Student Resource Si1r2! contains a number of ]inks and documents chat students may find useNI in their ongoing computer science education. The site includesx review of basic\_ rele '...ant mathematics; adviee on research, writing, and doing homework problems; links to computer science research resources, such as report repositories and bibliographies; and o[11,2r useful links

- An errata shed I:or the book, updated at most monthly

**COA** Courses

I he COA.5e Wet) s Le includes ]inks to Web sites for eours.cs mught using the book. These sites can provide lawful ideas about scheduling and topic ordering, as well a s a number of useful handouts and other mater 41Es.

### **Useful Web Sites**

The COAfic Web itc includes links to relevant Web sites. **The** links cover a broad spectrum Of iopics and will enable students to explore timely issues in greater depth;

## **Internet Mailing List**

An Internet mailing list is maintained so that instructors using this book can exchange information, sugge4...lions, and qUO;i1i0m. with each other and the ittLOOT. Subscription information is provided at the book's Web sill:.

## Simulation Tools for CA Projects

**'ihe** Web site includes links to the SintpkSo kir and WPC:ache Web .rites. These are two software packages that serve is frameworks for project iniplerncritalion. Each site includes downloadable software and background information. See Appendix C for more inrOrMatiOn.

## CONTENTS

Web Site for Computer Organization and Architecture, Sixth Edition vi Preface xv About the Author xxi

#### PART ONE OVERVIEW 1

#### CHAPTER 1 Introduction 3

- 1.1 Organizaticiii ind Arclitual:tre 4

- 1.2 Structure. and Function 5

- 1.3 Why study Computer OrAani.?..a.tion :and rch I e:et ate? 10

- 1.4 OLE.0110 ul li3C: Book<sup>•</sup>"LI

- 1.5 internet, and Web Resources

#### CHAPTER 2 Computer Evolution and Performance 15

- 2.1 A Bri(.21 HiNuor., ! of Computers 1(i

- 2.2 Designing ror Perform 77

- 2.3 Pentium Rod PowerPC Evolinion 41

- 2.4 Rucommended Relading and Web Sits 44

- 2.5 K.c.y k.eview. Ouestion8, and Problems 45

#### PART TWO THE COMPUTER SYSTEM 47

| CFLAPTER 3 | A '.17 op-Levei View of Computer Function |

|------------|-------------------------------------------|

|            | and Interconnection 49                    |

|            |                                           |

- 3.3 Computer Components 5(1

- 3.2 Computer Function 53

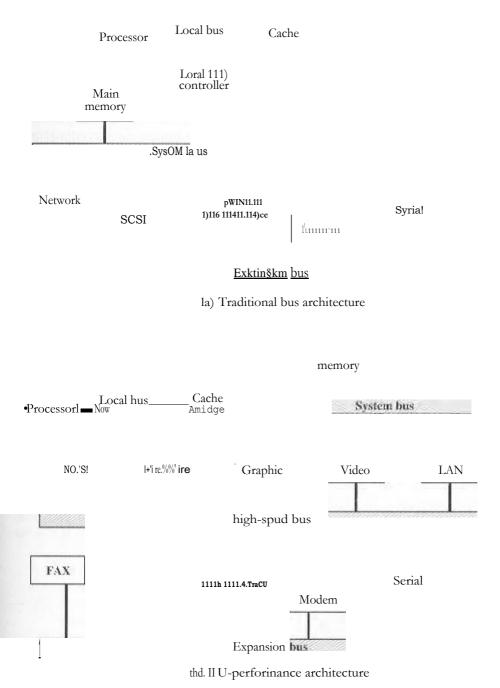

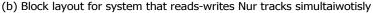

- 3.3 Interconnection Structiii.s

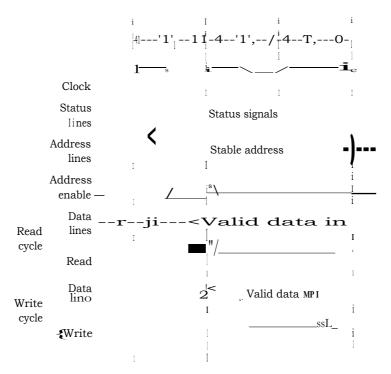

- 3.4 Bus Interconnection 69

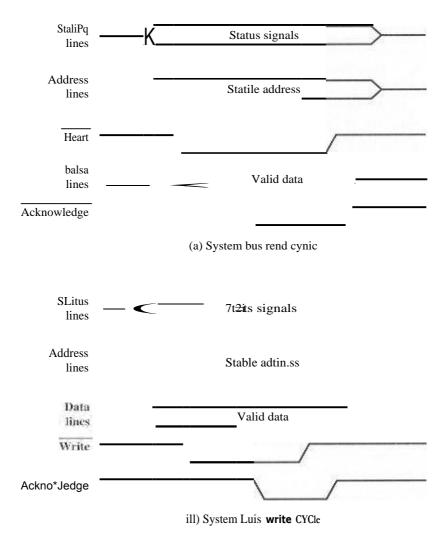

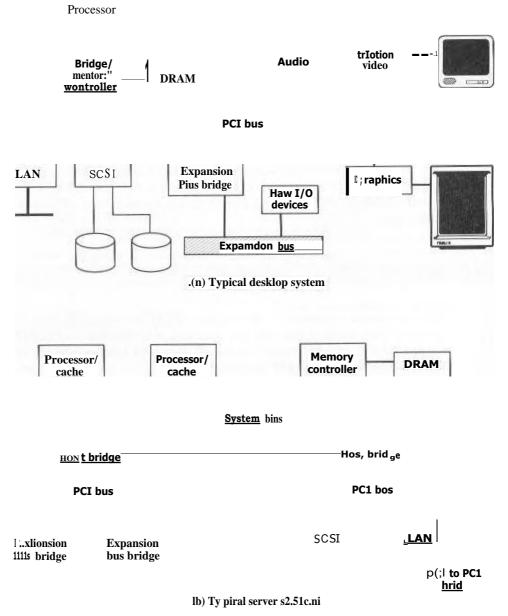

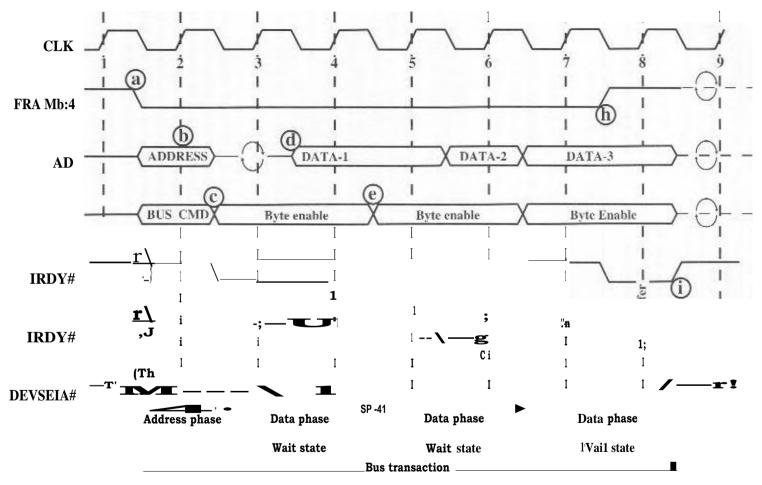

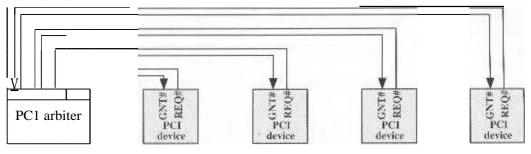

- 3.3 P('1 79

3.6 Reconimendc4 Reading and Well Sites 89 3.7 Key Terms, Review Quic,tionz;,, 4,nd Problems 90 Appendix 3A: Timinr2. Diagrams 92

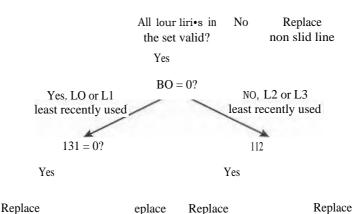

#### CHAPTER 4 Cache Memory 95

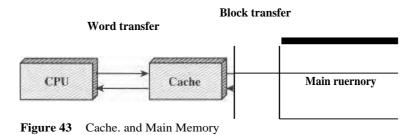

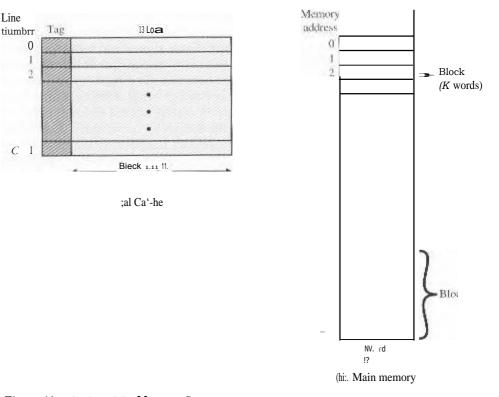

- 4.1 Computer Memory SysLarn Overvivw 964.2. Cache Memory Principles. 1{13

- deElenIN of CEIChC DOSigri. 106

4.4 Poruium 4 rind PowErPC Cache Organizations 121 4,5 Recommended Rc2adirtg 125

Kcy Terms, Review Questions. and Problcins 125 Appendix 4A; Puu1'orm41].}ce. Characteristics of Two-Le•el N1.-...ral.nes 128

#### CHAPTER 3 Internal Memory 137

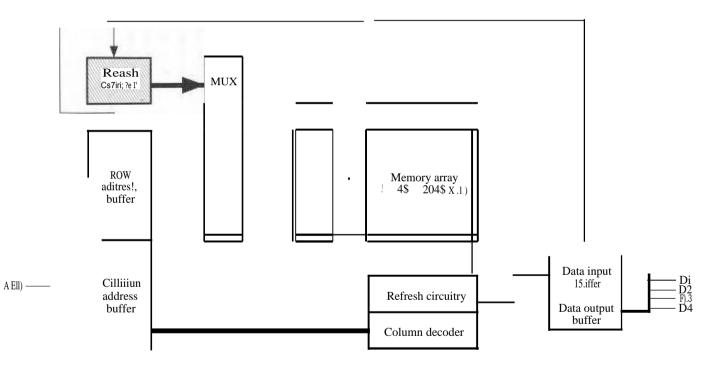

- 5,1 Semiconductor Main Memory 138

- 52 Error Correction 148

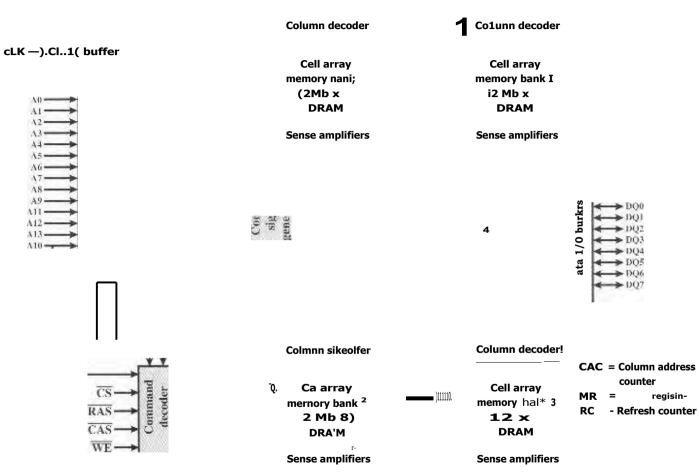

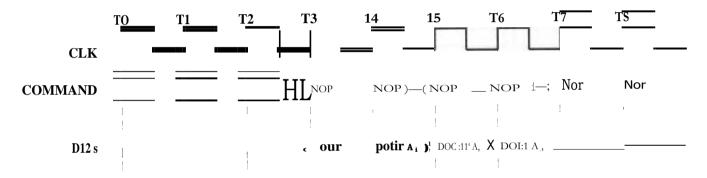

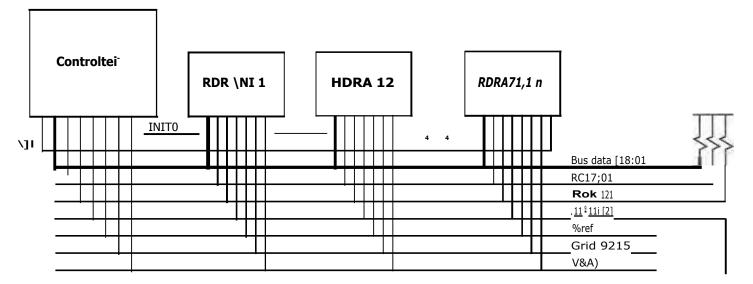

- 5.3 Advanced DRAM Organization 154

- 5,4 Recommended Reading and Web Sites 159

- 55 Key Terms, Review Questions. and 2m, 16)

#### CHAPTER 6 Exteenal Memory 163

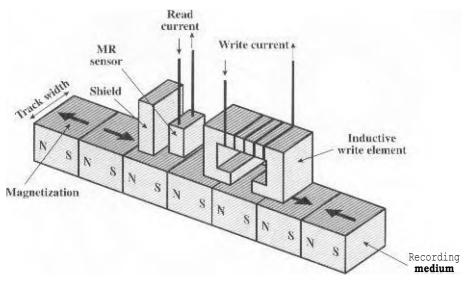

- 6,1 Magnetic Disk 164

- 6.2 R,A.II3 174

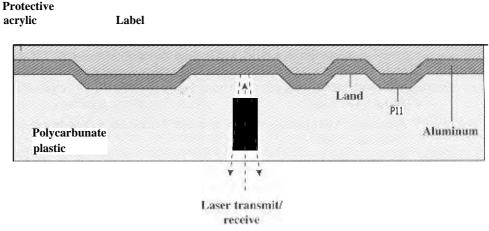

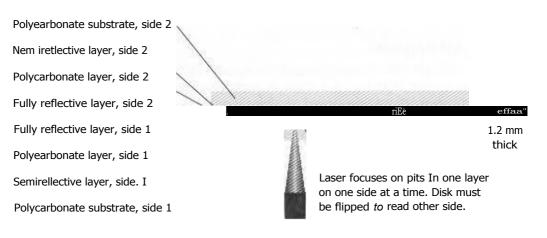

- 6.3 Opticai Memory 184

- 6.4 Magnetic Tape 189

- 6.5 Reconirnended Reading and Web Sites 191

- 6:6 Key Terms, Review Questions, d Problems 192

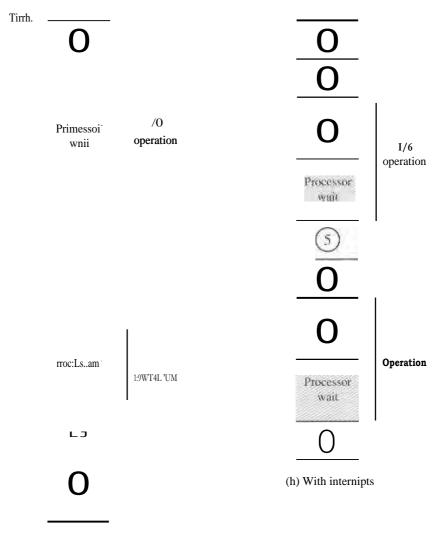

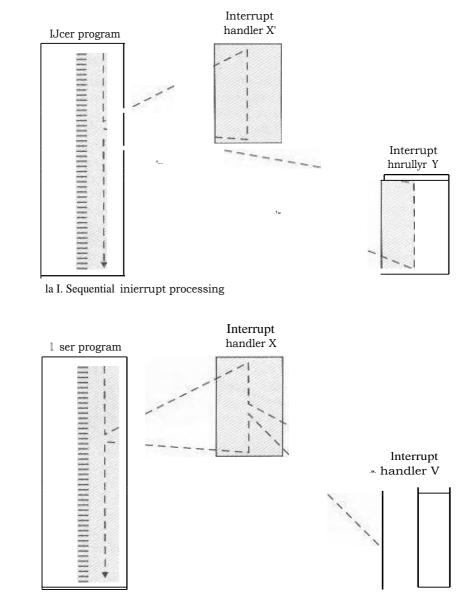

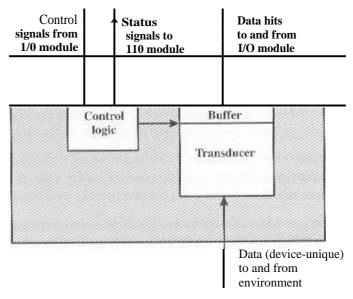

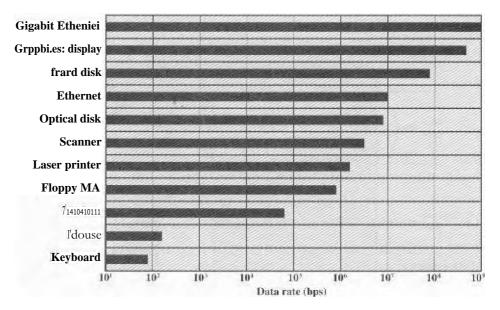

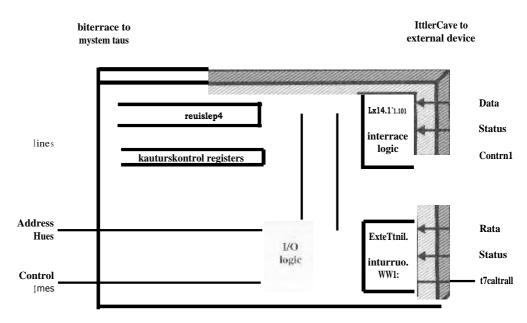

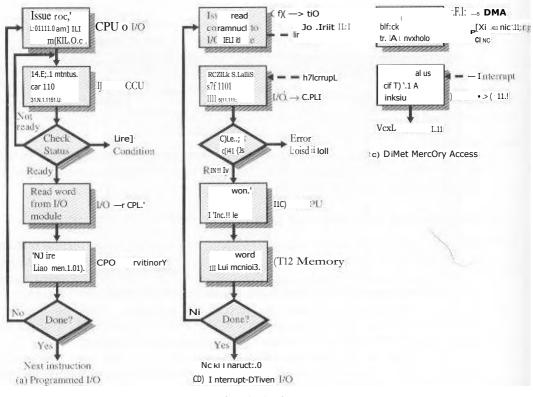

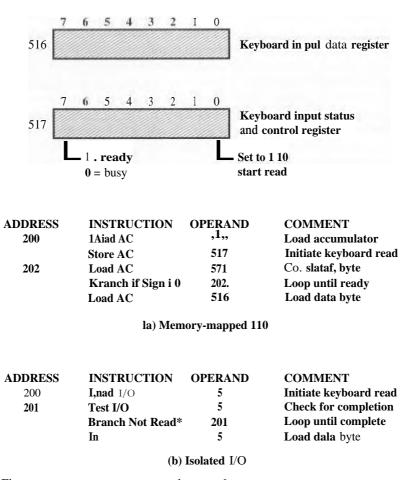

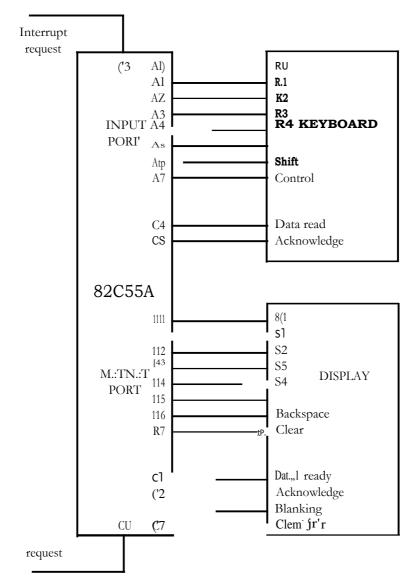

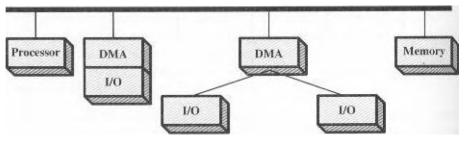

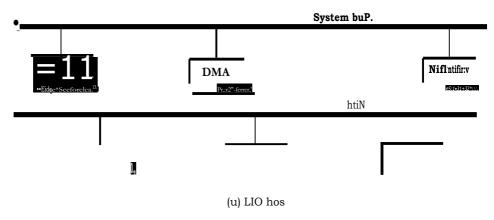

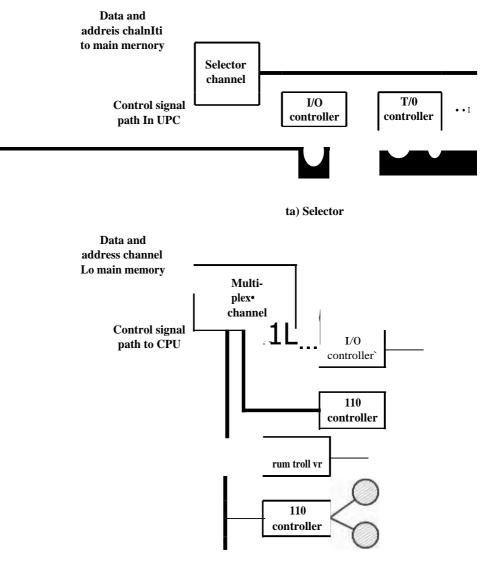

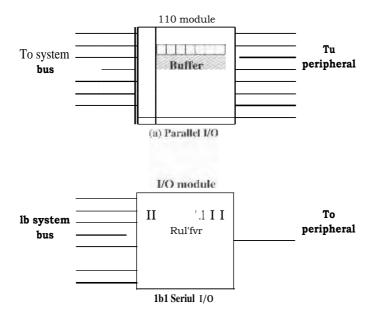

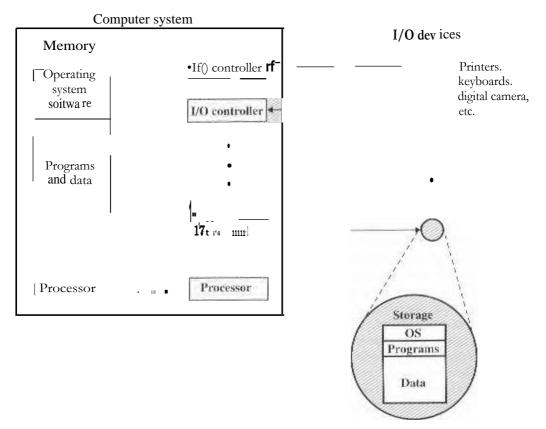

#### CHAPTER 7 Input/Output 195

- 7.1 Exlernal Devices 197 110 Modules 201

- 7.3 Programmed I/O 204

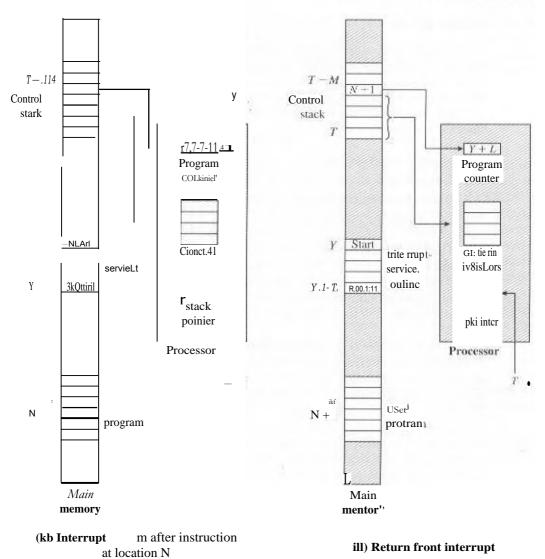

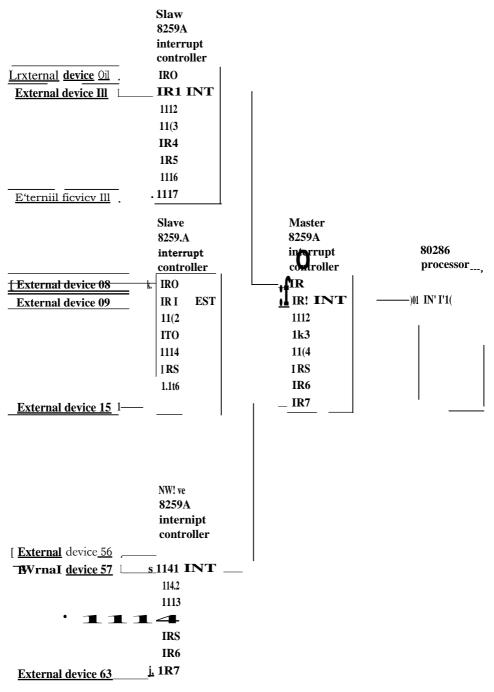

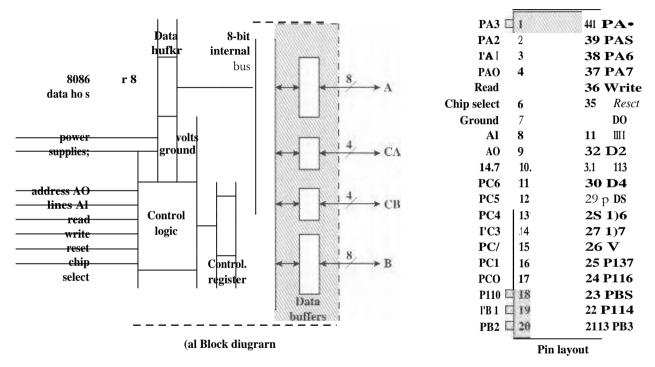

- 7.4 Interrupt-Driven I.10 2.08

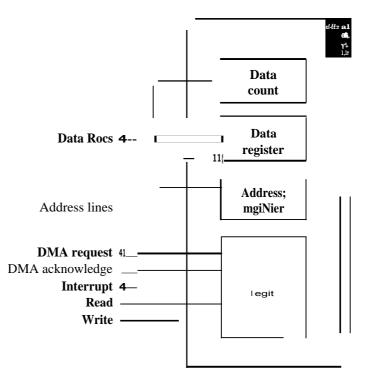

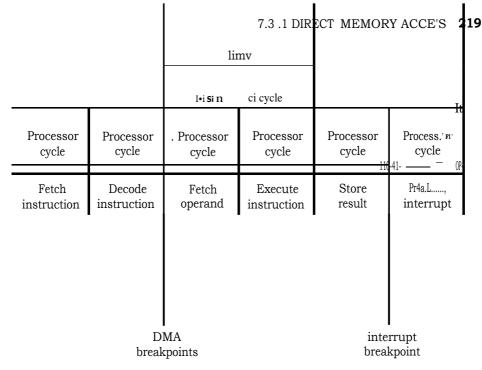

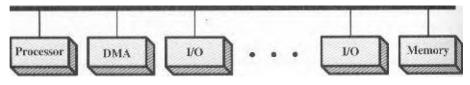

- 7.5 Direct Memory Aecuss 216

- 7.6 I/O Channels and Processors 220

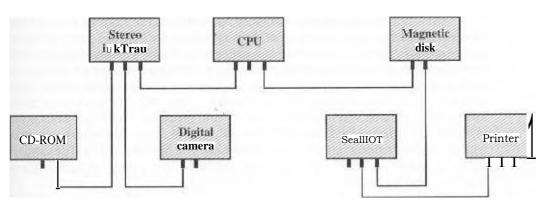

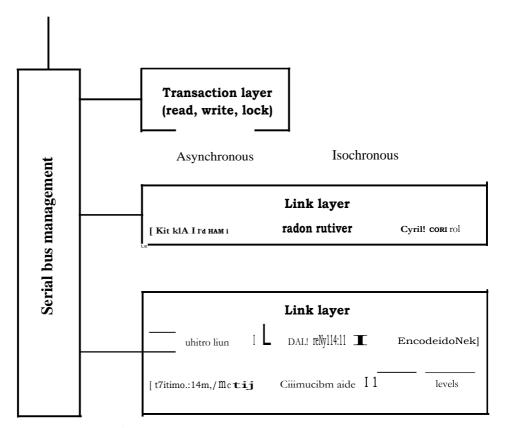

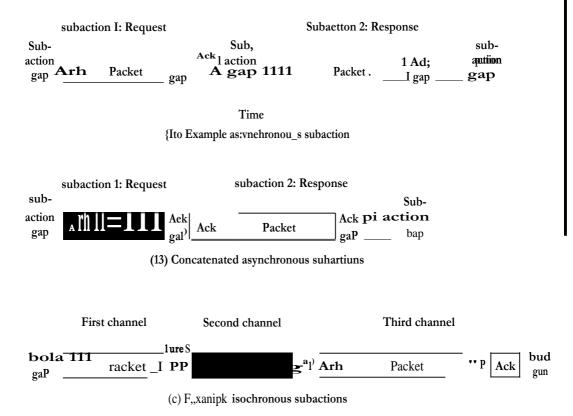

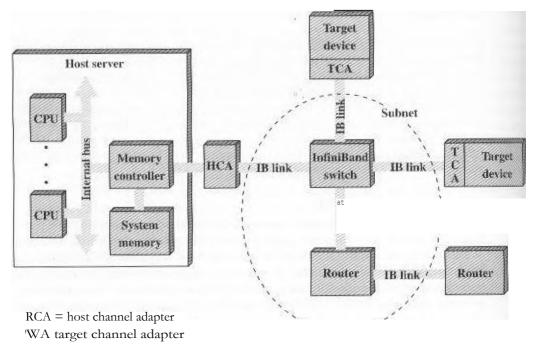

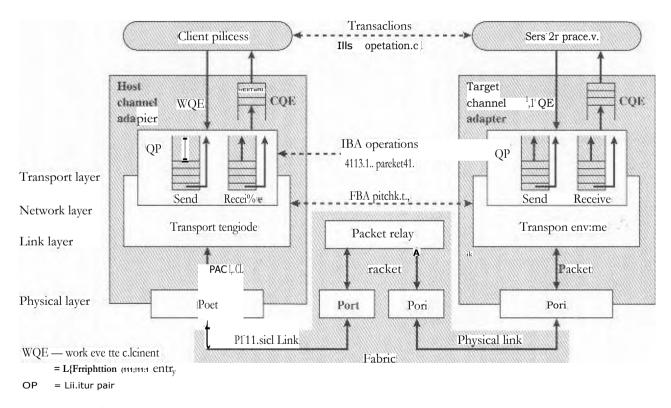

- 7.7 The External Interface: FireWirc kind InfiniBand 223

- 7.8 Recommended Reading and Web Sites 233

- 7,9 Key '1'crTns, Review Questions, and Problems 233

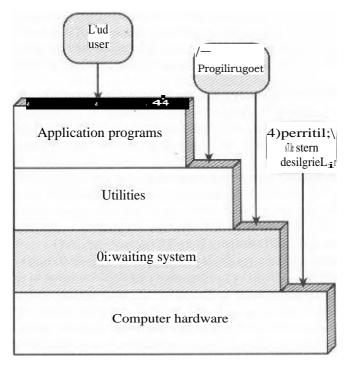

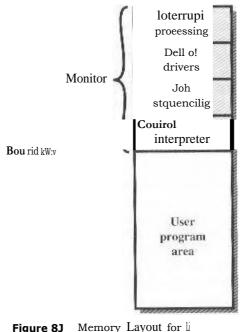

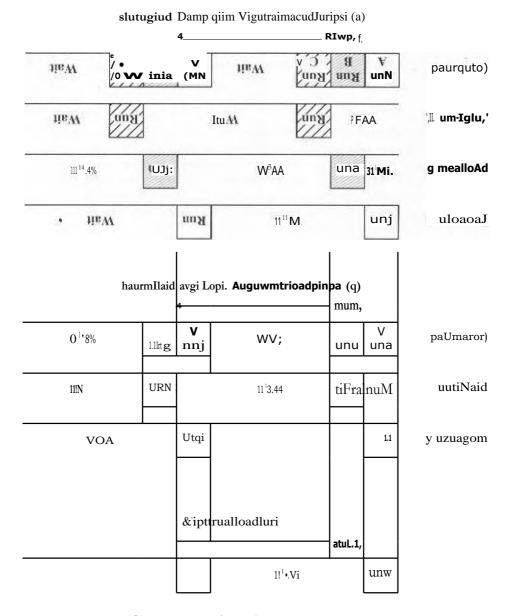

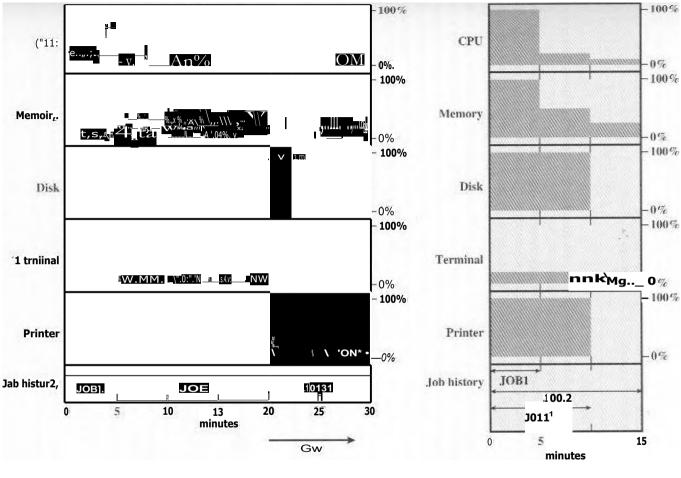

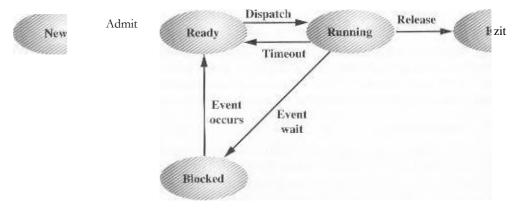

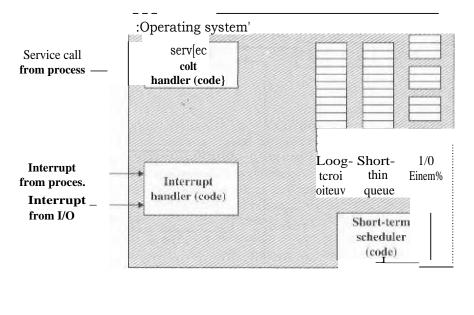

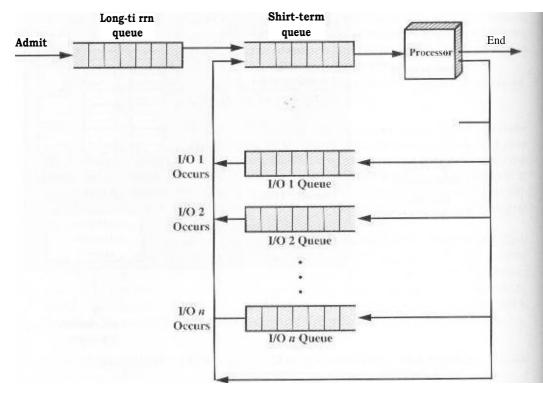

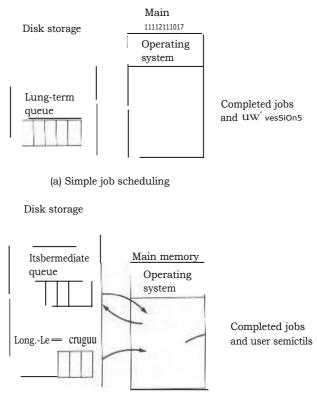

#### CHAPTER 8 Operating System Support 237

- 8.1 Operating System Overview 28

- 8.2 Scheduling 250

- 8.3 Memory Management 256

- 8,4 Pentium 11 and PowerPC Memory Management 269

- 8.5 Recommended Reading and Web Sites 277

- 8,6 Kcy 'Ferms, Review Questions, and Problems 278

#### PART THREE THE CENTRAL PROCESSING UNIT 281

#### **CHAPTER 9** Computer Arithmetic 283

- 9.1 The Ariihrne(ie and Logic Unit 284

- 2 Integer Representation 285

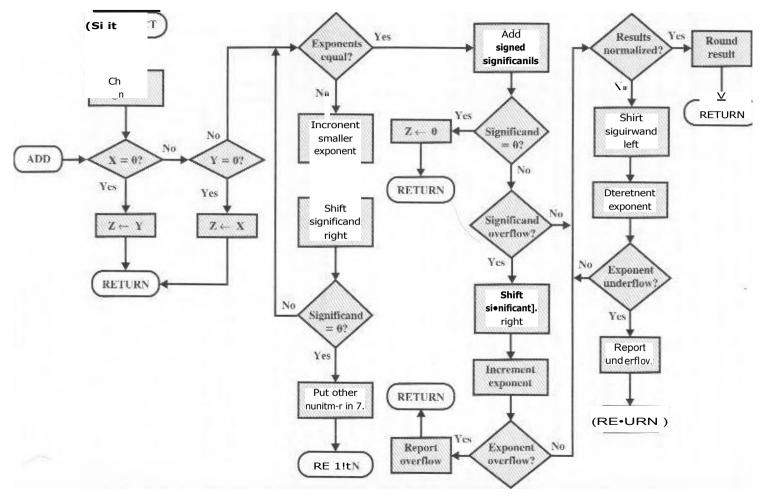

- 9.3 Integer Arithmetic 29]

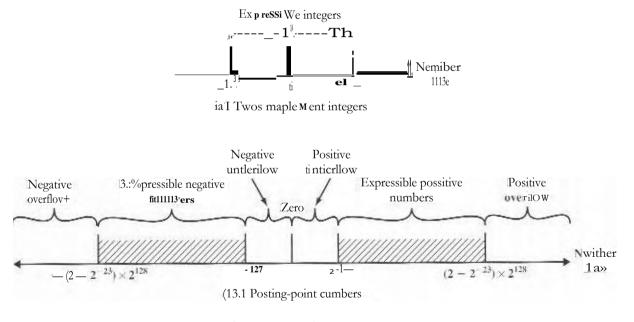

- 9.4 Flooring-Pin Representation 307

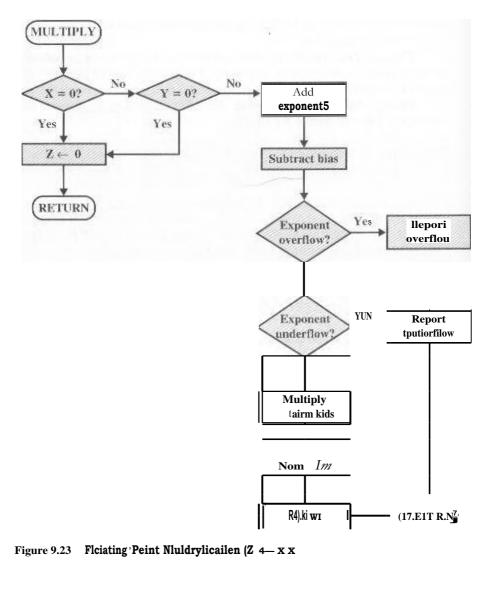

- 9.5 Floating-Point Arithmetic 333

- 9.6 Recommended Reading and Web Sites 324

- 9.7 Key Terms, Review Questions, and Problems 325

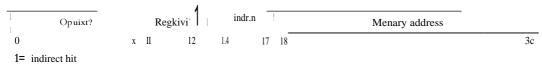

#### CHAPTER 10 Instruction Sets: Characteristics and Functions 329

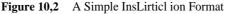

Machine Instruction Characteristics 330 10.2 Types or Operands 337 10.3 Pentium anti PocketPC Data Types 339 10.4 Types of Opor; iiions 341 10.5 Pentium and PowerPC Operalion Types 355 10.6 Asscribty Language. 364 10.7 Recommended Reading 366 111.8 Key Terms, Review Questions, and Problems 360 Appendix IOA, Stacks 371 Appendix 10H.: Little-, Big-, and Bi-Eridian 376

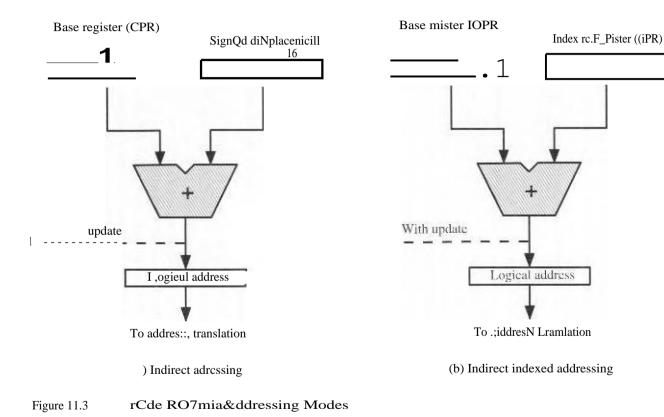

#### CHAPTER 11 Instruction Sets: Addressing Modes and Formats 381

- 11.1 Addressing 382

- 11,2 Pentium 111(1 PowerPC Addressing Modes 359

- 11.3 Instruction Formats 395

- 11.4 Pentium and PowerPC Instruction Formats 404

- 11.5 Recommended Rending 408

- 11.6 Key 'Terms, Review Questions, rand Problems 409

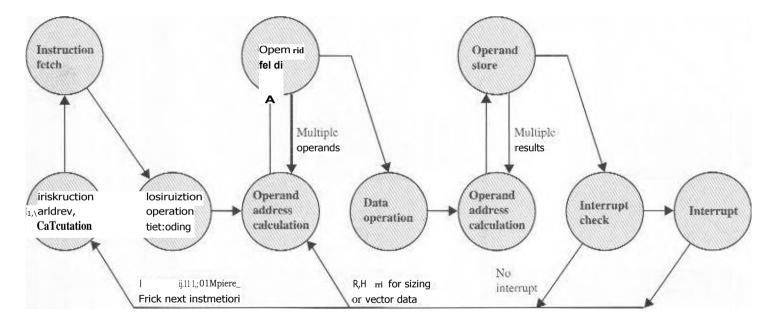

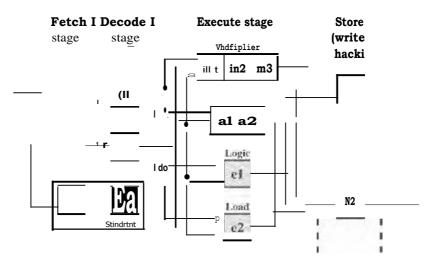

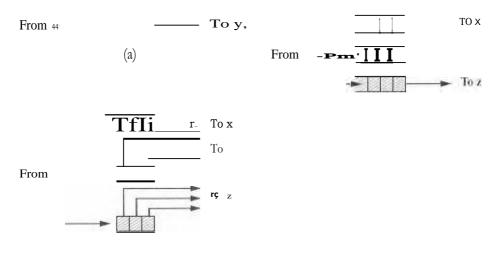

#### **CHAPTER 12 CPU Structure and Function 411**

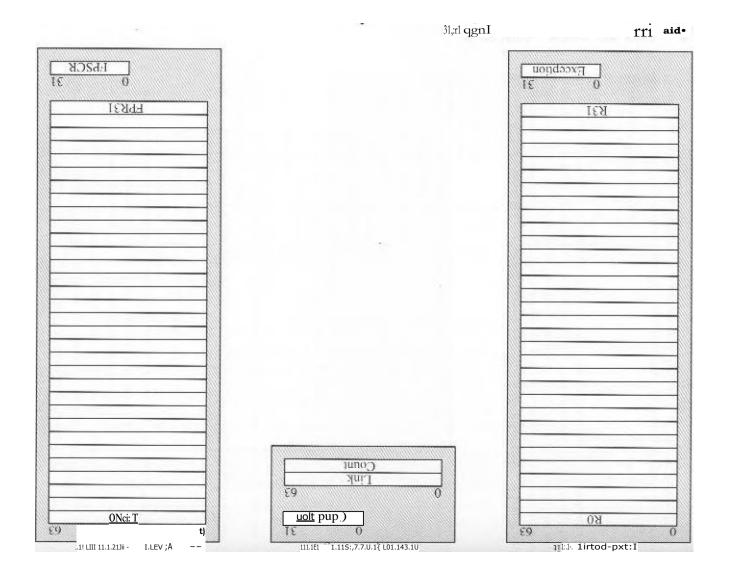

- 12.1 Processor Organization 4[2

- 12.2 Register Organization 414

- 12.3 Instruction Cycle 420

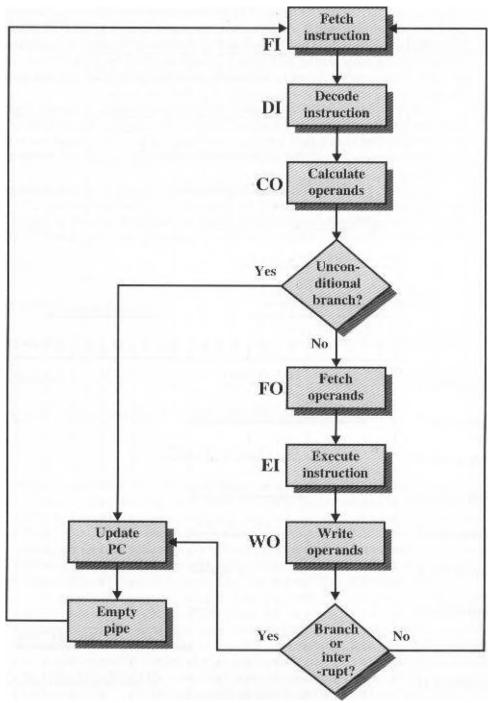

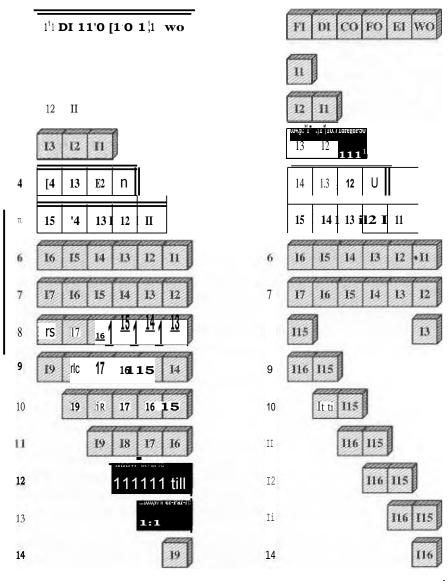

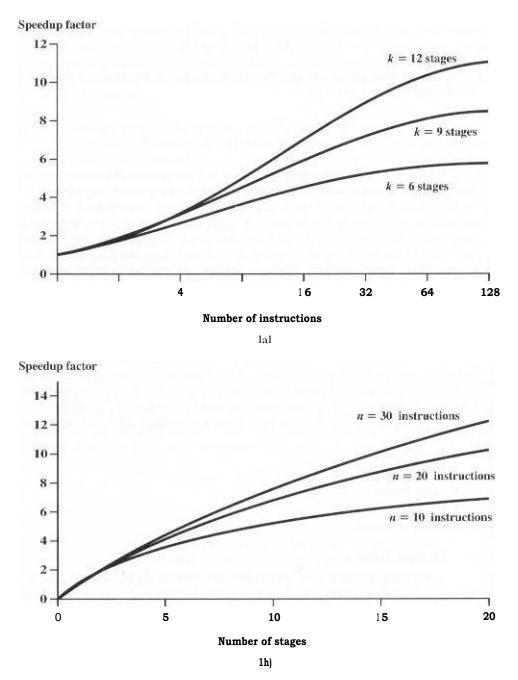

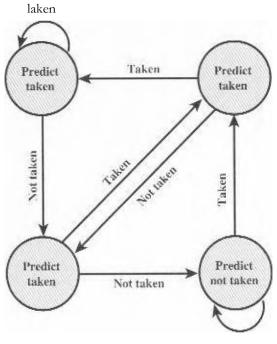

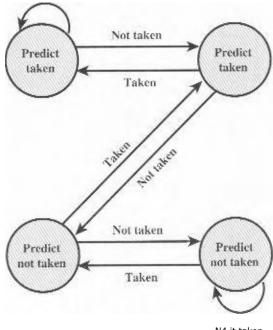

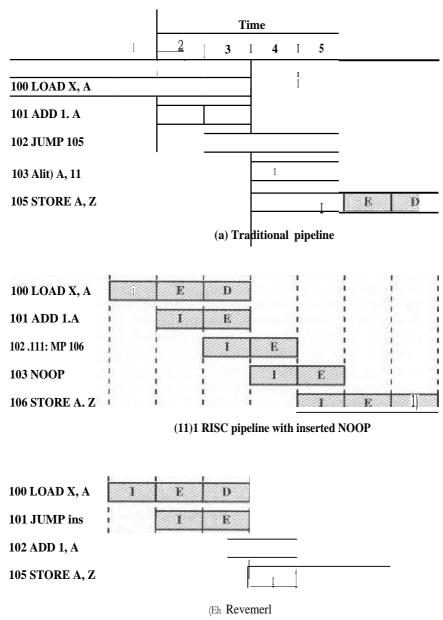

- 12.4 Instruction Pipelining 424

- 12.5 'The Pentium Processor 440

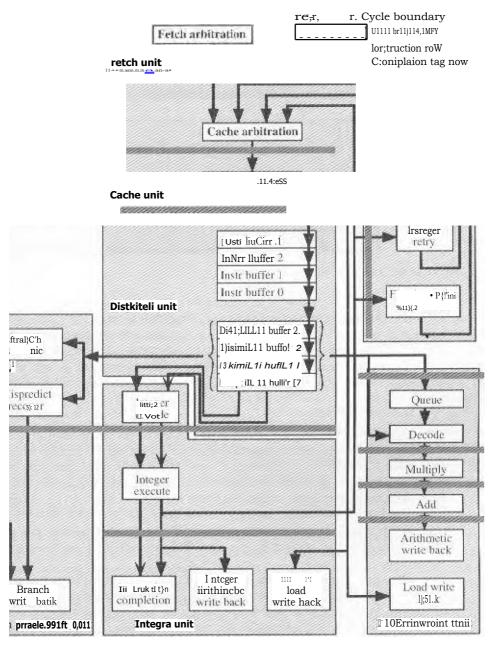

- 12.6 The PowerPC Processor 430

- 12,7 Recommended Reading 457

- 12.H Key Terms. Review Questions, and Problems 458

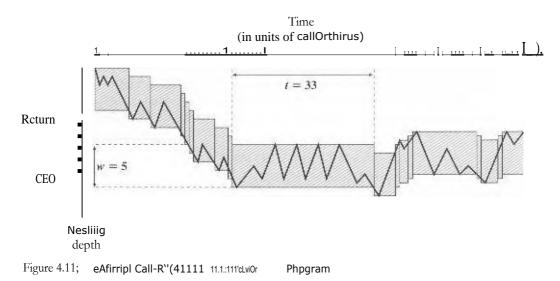

#### CHAPTER 13 Reduced Instruction Set Computers 461

- 13.1 Instruction 1-: Necution Characteristics 463

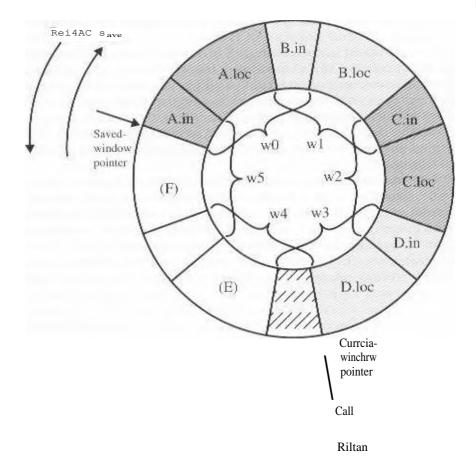

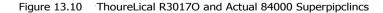

- 13.2 The Use of a Large Register Fite 467

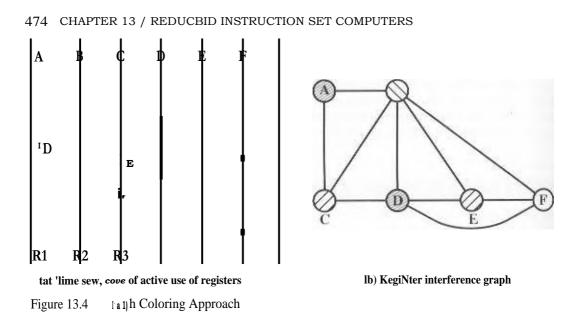

- 13.3 Compiler-Based Register Optimization 473

- 13.4 Reduced Instruction Set Areill Cod 'Luc. 474

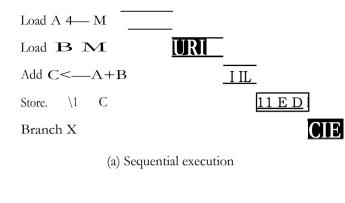

- 13.5 RISC Pipelining 482

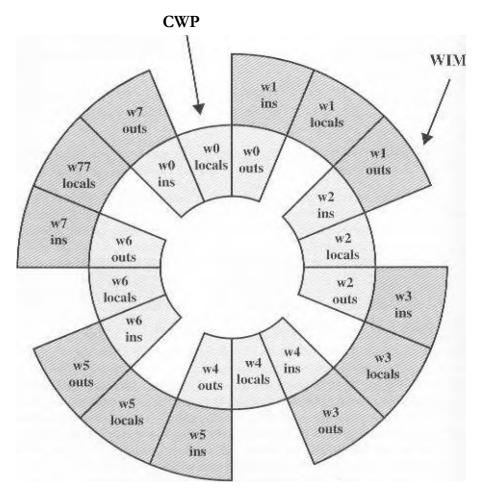

- 13.6 MI PS 84000 486

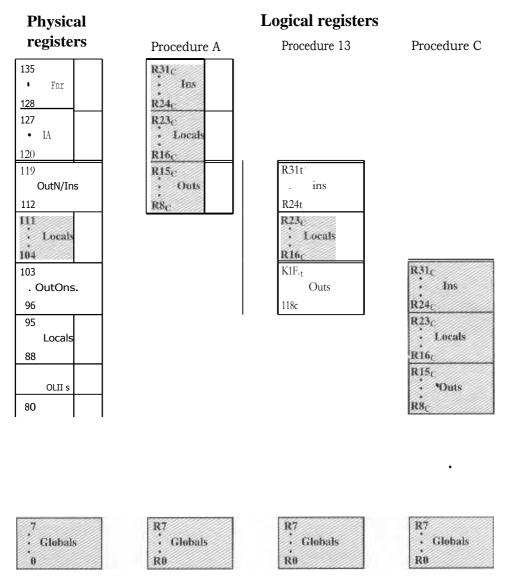

- 13.7 SPARC 494

- 13.8 RISC versus C1SC: Controversy 500

- 13.9 Recommended Reading 501

- 13.10 Key Turns, Review Questions, and Problems 502

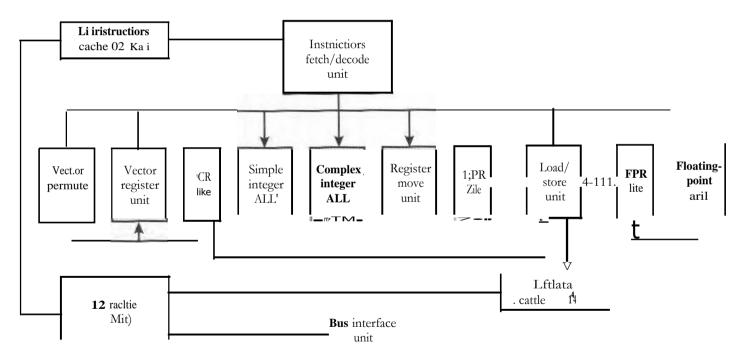

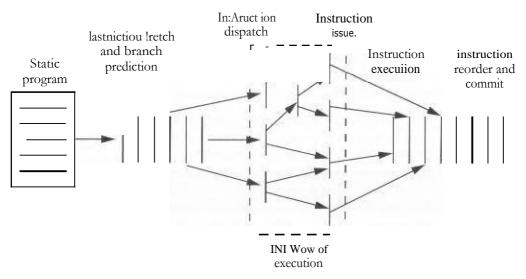

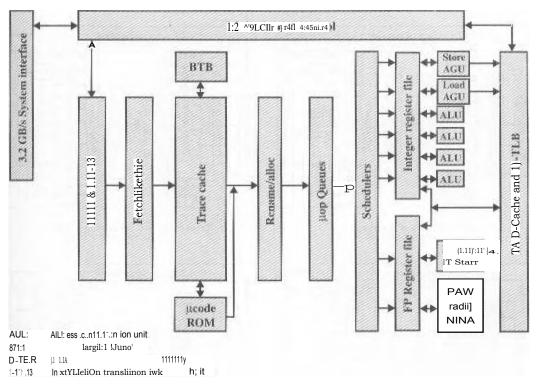

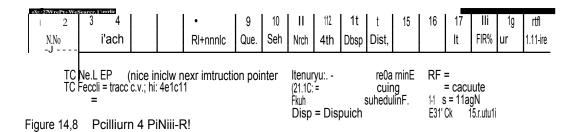

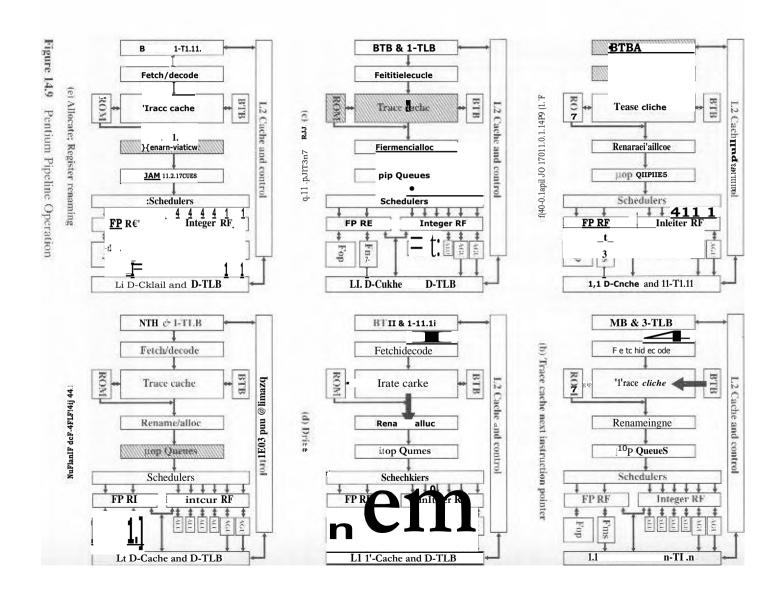

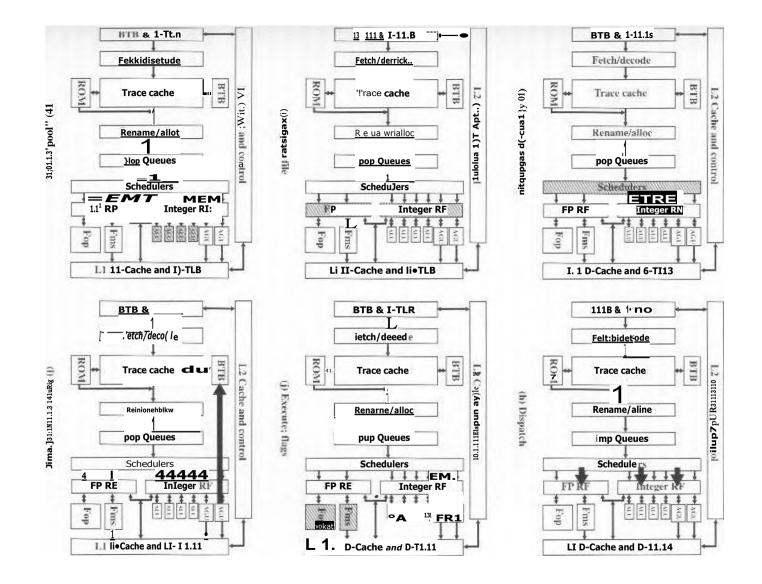

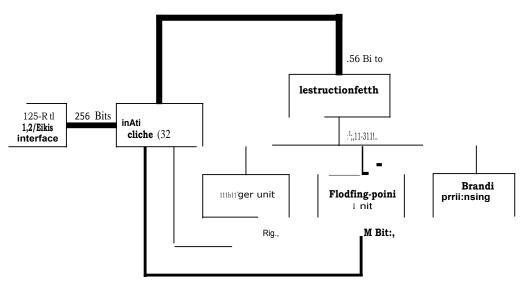

#### CHAPTER 14 Instruction-Level Parallelism and Superscalar Processors 50

- 14.1 Overview 507

- 14.2 Design Issues 511

- 14.3 Pentium 4 520

- 14.4 PowerPC 527

- 14.5 Recommended Reading 535

- 14.6 Key Terms, Review Questions, and Problems 536

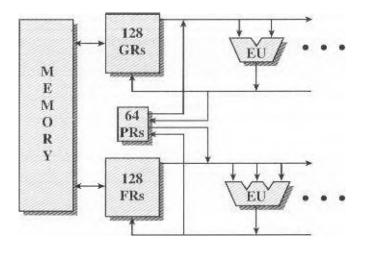

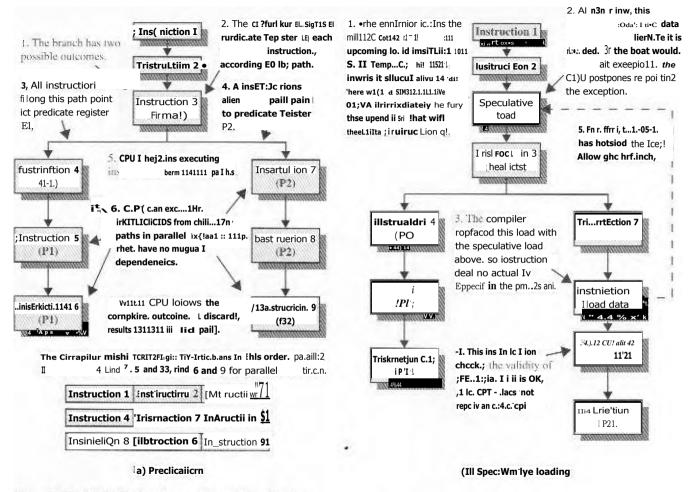

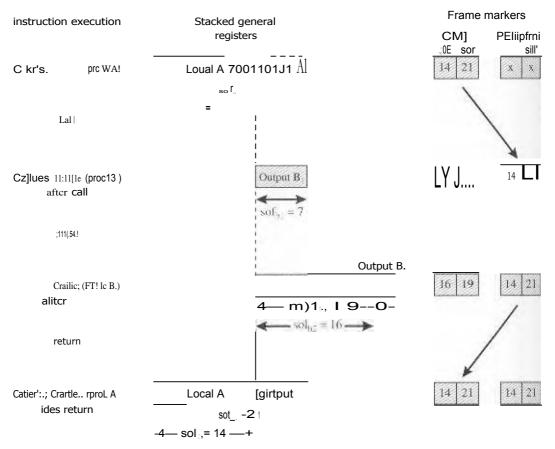

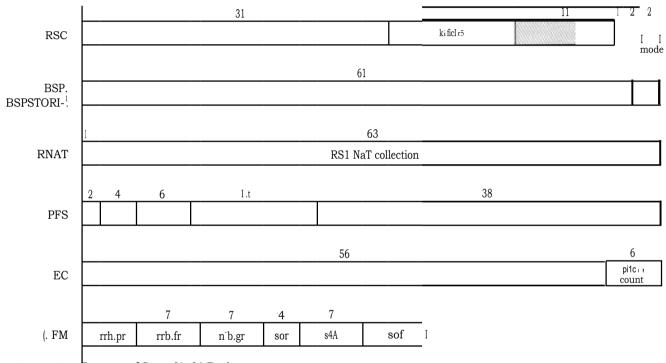

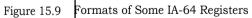

#### CHAPTER 15 The 1A-64 Architecture 541

- 15.1 Motivation 543

- 15.2 General Organization 544

- 15.3 Predication, Speculation, and Software Pipelining 546

- 15.4 1A-64 Instruction Set Architecture 563

- 15.5 Itanium Organization 568

- 15.6 Recommended Reading and Web Sites 569

- 15.7 Key Terms, Review Questions, and Problems 570

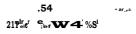

#### PART FOUR. THE CONTROL UNIT 573

#### **CHAPTER 16 Control Unit Operation 575**

- 161 Micro-Operations 577

- 16.2 Control of the Processor 583

- 16.3 Hardwired Implementation 594

- 16.4 Recommended Reading 597

- 16.5 Key Terms, Review Questions, and Problems 597

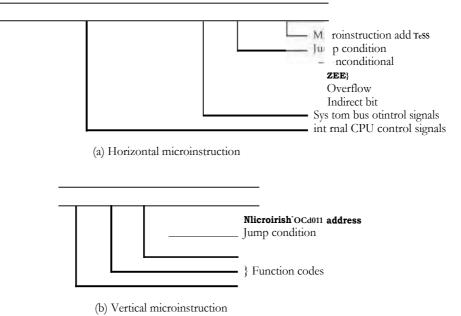

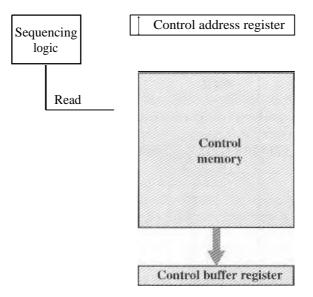

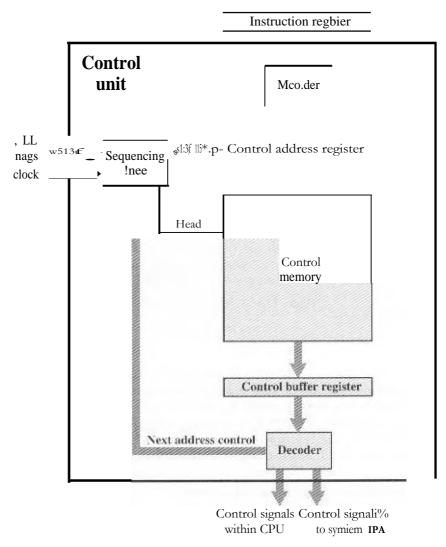

#### CHAPTER 17 Microprogrammed Control 599

- 17.1 Basic Concepts 600

- 17.2 Microinstruction Sequencing 609

- 17.3 Microinstruction Execution 615

- 17.4 1 1 SW} 627

- 17.5 Applications of Microprogramming 637

- 17.6 Recommended Reading 638

- 17.7 Key Terms. Review Questions. and Problems 639

#### **PART FIVE PARALLEL ORGANIZATION 641**

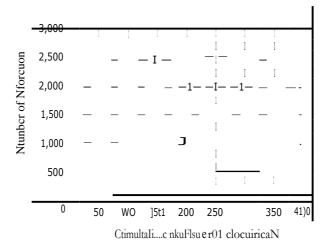

#### **CHAPTER 18 Parallel Processing 643**

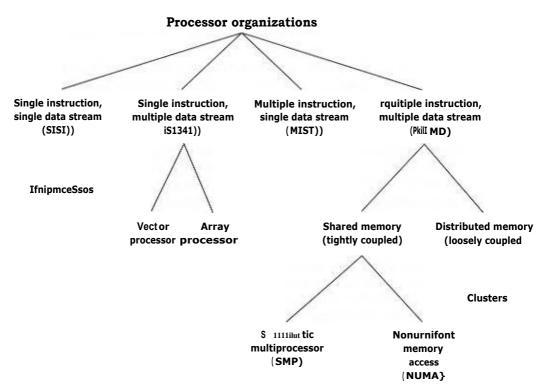

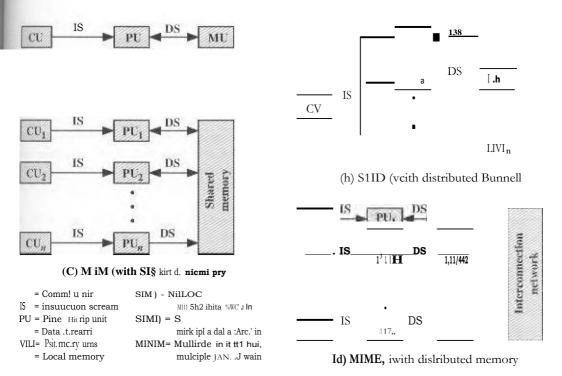

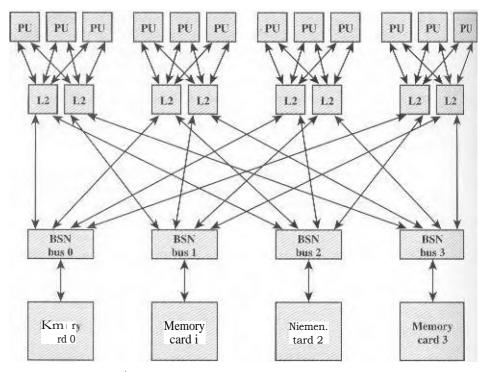

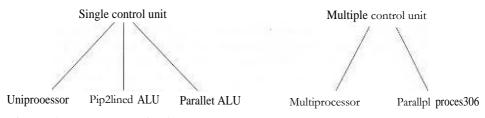

- 18.1 rdultiple Processor Organizations 645

- 18.2 Symmetric Multiprocessors 647

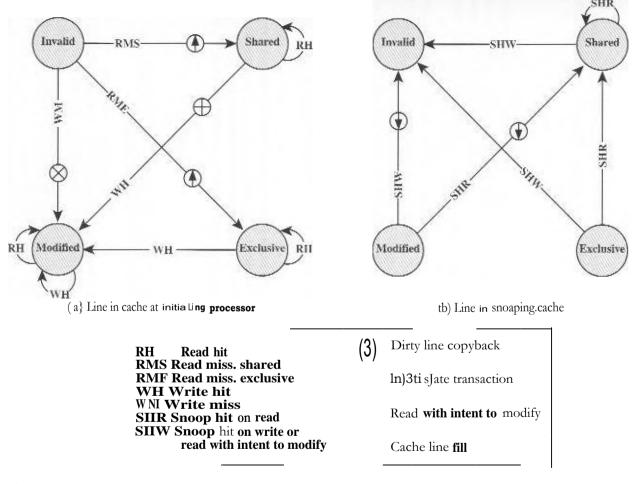

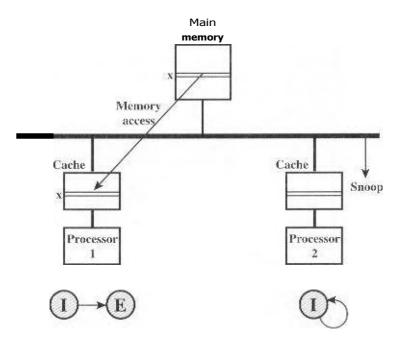

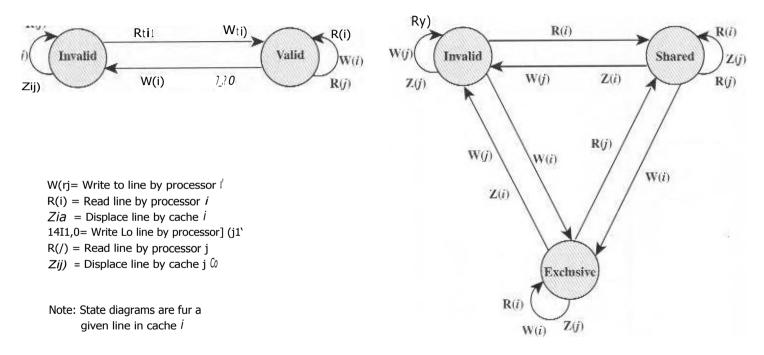

- 18.3 Cache Coherence and the MESI Protocol 656

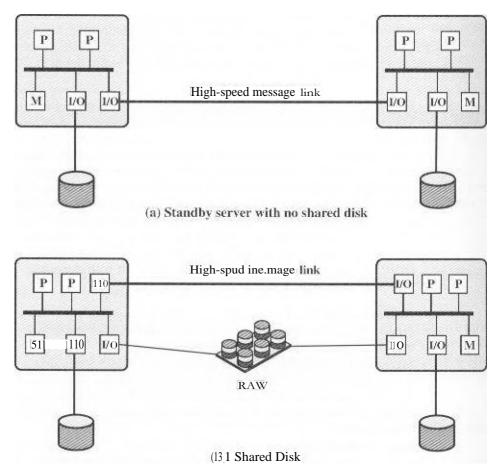

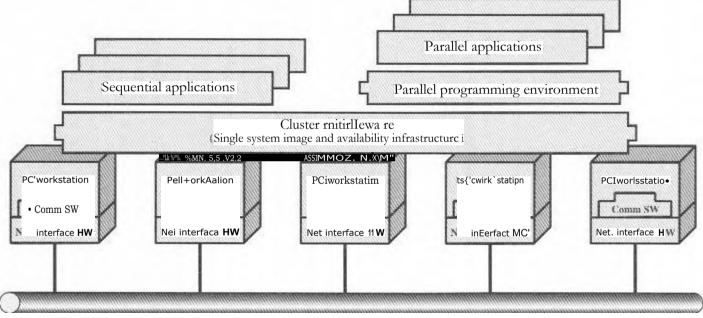

- 18.4 Clusters 663

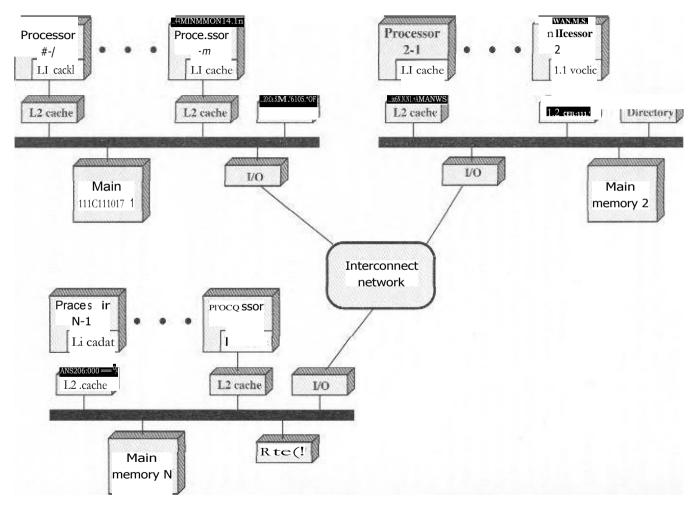

- 18.5 Nonuniform Memory Access 670

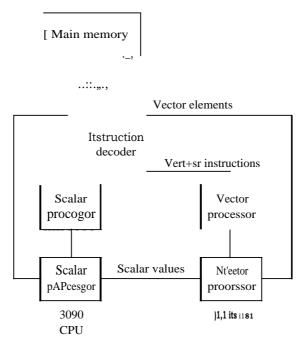

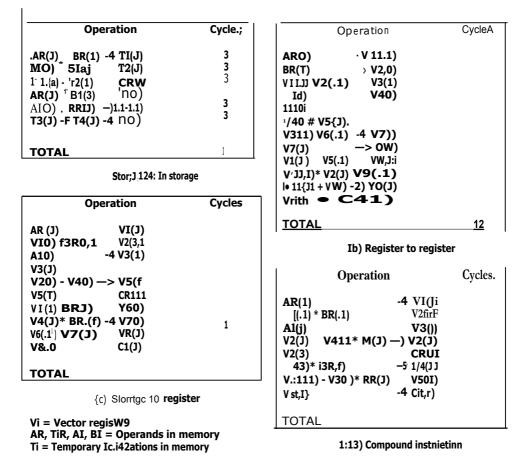

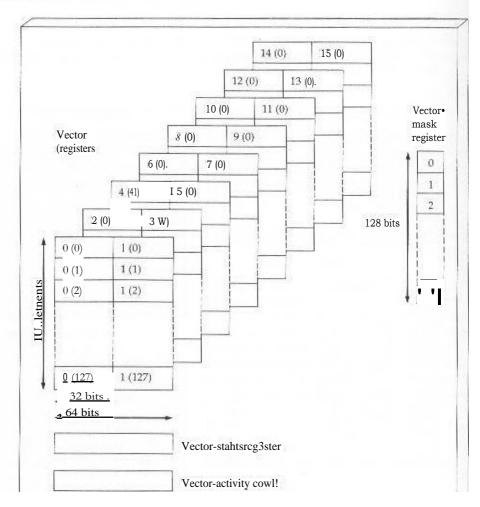

- 18.6 Vector Computation 674

- 18.7 Recommended Reading 687

- 18,8 Key Terms, Review Questions, and Problems 688

#### APPENDICES

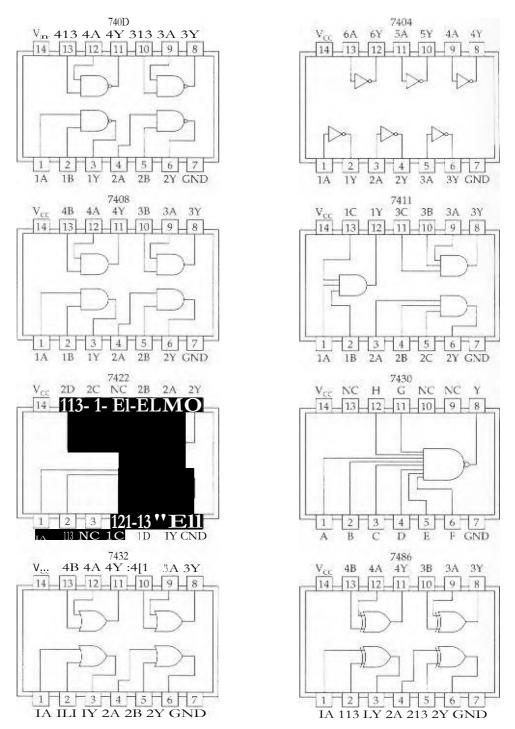

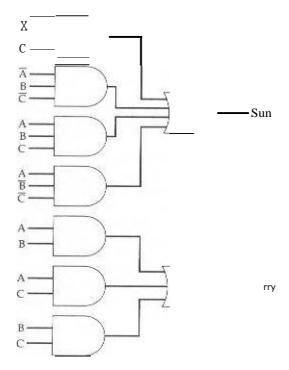

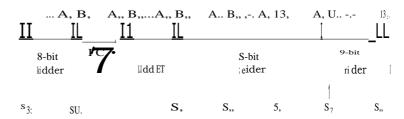

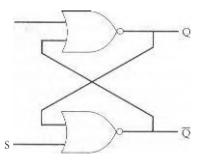

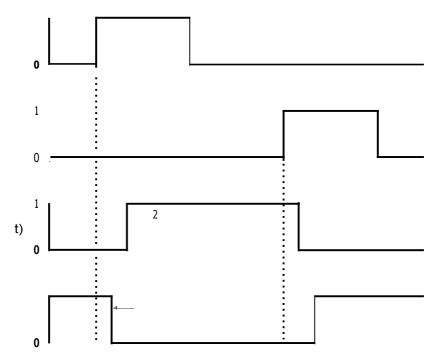

APPENDIX A Digita/ Logic 693

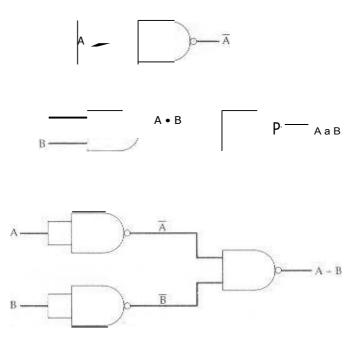

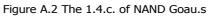

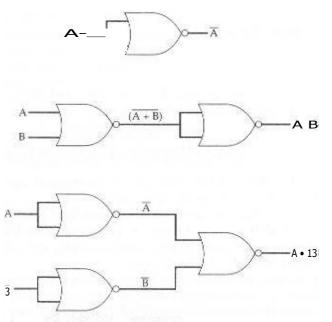

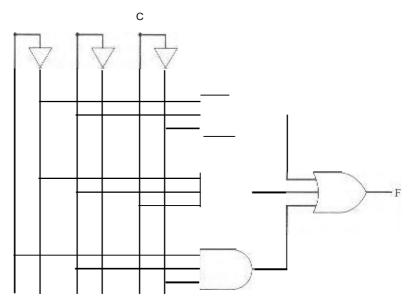

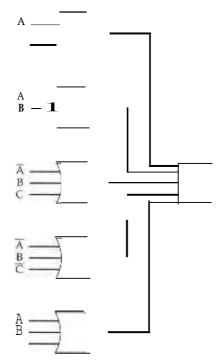

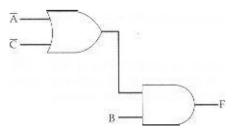

A.1 Boolean Algc4 Fr4i 694

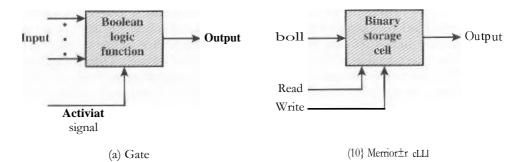

A.2 Gates 696

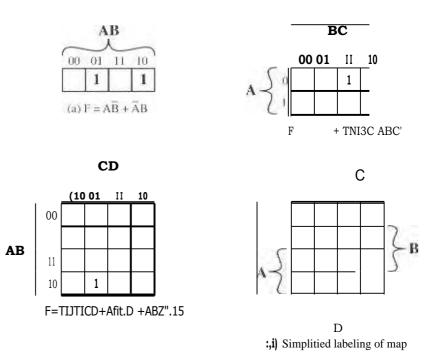

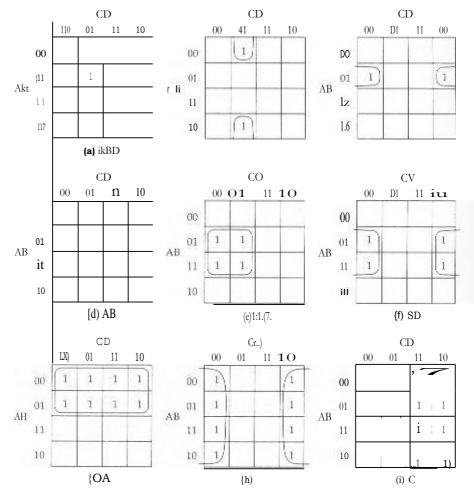

.A1 Corn binational Circuits 699

A.4 Sequential Circuits 720

A,5 Problems 7:O

#### APPENDIX B Number Systems 733

B.I. The Decirrml Sp.licui 734

11,2 The Binary System 734

B.3 Converting between Binary and Deein-A 7.3.5

BA I lexackeirmil Notation 73

13.5 Problems 739

#### APPENDIX C Projects for Teaching Computer Organization and Architectute 741

C.1 Re.7<sup>(2)</sup> 1rat Projects 742 C.2 Simulation Projects 742 C.3 Reading/Report Assignments **743**

#### **GLOSSARY** 745

#### **REFERENCES 757**

#### **INDEX 773**

## PECEFACE

bOok is about the structure and function of computers. Its purpose is to present. as clearly and completely as possible, the nature and characteristics of modern-day computer systems.

rhis task is challenging for several re, sans. I first, there is a tremendous variety of products that can rightly claim the name of computer, from singlechip microprocessors costing a tcw dollars to supercomputers costing tens of millions of dollars. Variety is exhibited not only in cost, but in size. performance, and .application. Second, the rapid pace of change that has always characterized computer technology continues with no letup. These changes cover all aspects of computer technology, from the underlying integrated circuit technology used to construct computer components, to the increasing use of parallel organization concepts in combining those components.

In spite of the pariety and pace of change in the computer field. certain fundamental concepts apply consistently throughout. The application of these concepts depends on the current state of the technology and the pricelperformanc.e objectives of the designer. The intent of this hook is to provide a thorough discussion of the fundamentals of computer organization and architecture and to relate these to contemporary design issues.

The subtitle suggests the theme. and the approach taken in this book. It has always been important to design computer systems to achieve- high performance, but never has this requirement been stronger or more difficult to satisfy than today. All of the basic performance characteristics of computer systems, including processor speed, memory speed, memory capacity, and interconnection data rates, are increasing rapidly. Moreover• they are increasing ait different rates. This makes it difficult to desiv,rn a balanced system that maximizes the performance and utilization of all elements. 'Thus, computer design increasingly becomes a game of changing the structure or function in one area to compensate for a performance mismatch in another area. We will see this game played out in numerous design decisions through. out the book. A computer system, like any syStem, consists of an interrelated set of components. The system is best characterized in terms of structure—the way in which components are interconnected—and function—the operation of the individual components. Furthermore, a computer's organization is hierarchical. Each major component can be further described by decomposing it into its major subcomponents and describing their structure and function. For clarity and ease of understanding, this hierarchical organization is described in this hook from the top down:

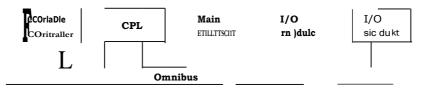

- Computer System: Major components are processor. memory. and 1/0.

- Processor. Major components are control unit. register, A1.1), and instruction execution unit.

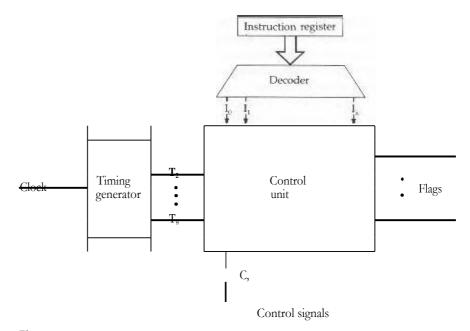

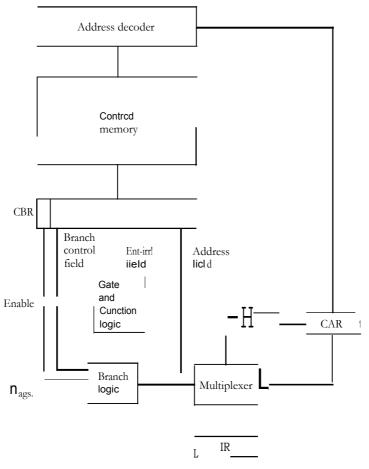

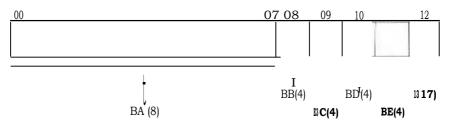

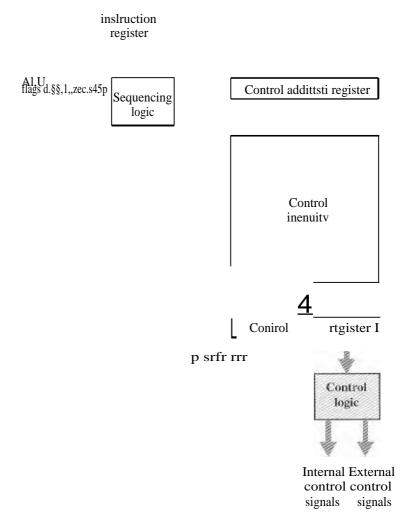

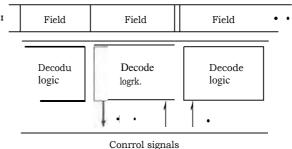

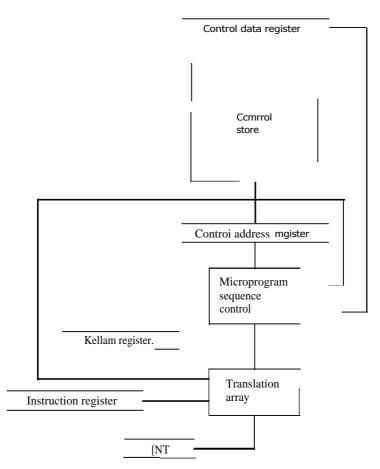

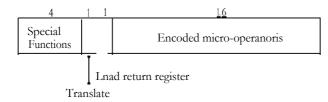

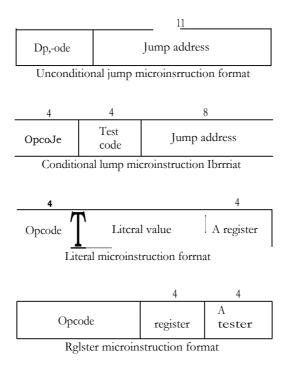

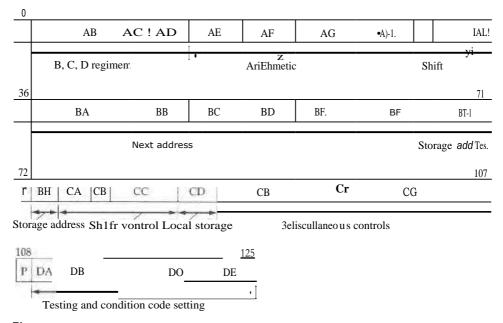

**Control Unit:** Major components are control memory, microinstruction sequencing logic, and registers.

The objective is to present the material in a fashion that keeps new material in a clear context. This should minimize the chance that the reader will get lost and should provide better motivation than a bottom-up approach.

Throughout the discussion, aspects of the system are viewed from the points of view of both architecture (those attributes of a system visible to a machine language programmer) and organization (the operational units and their interconnections that realize the architecture).

#### EXAMPLE SYSTEMS Ardr<sup>u, 47</sup>. 4

Phis hook uses examples from a number of different machines to clarify and reinforce the concepts being presented. Many, but by no means all, of the examples are drawn from two computer families: the Intel Pentium 4, and the IBWMotorola PowerPC. These two systems together encompass most of the current computer design trends. The Pentium 4 is essentially a complex instruction set computer (CISC) with some RISC Features. while the PowerPC is essentially a reduced instruction set computer (RISC). Both systems make use of superscalar design principles and both support multiple processor configurations.

#### PLAN OF THE TEXT

The book is organized into live parts:

**Part One\_\_\_Overview: This part provides a preview and context** for **the** remainder of the book.

**Part Two\_\_\_The Computer System:** A computer system consists of processor, memory, and 110 modules. plus the interconnections among these major components. With the exception of the processor, which is sufficiently complex to he explored in Part Three. this part examines each of these elements in turn.

Part Three—The **Central Processing Unit:** The CPU consists of a control unit, reaisters, the wirhrricikl and logic unit, the instruction execution unit, and the interconnections among these components. Architectural issues, such as i nstruelion sot design and data types, are covered, Part Three also Jooks at orLianiy.a-tional issues, such as pipelining.

**Part Four—The Control Unit:** The control unit is that part of the processor that aciivales the various components of the processor. This part looks at the functioning of the control unil and its implementation using microprogramming. **Part Five—Parallel Organization:** This final part looks at some of the issues

involved in rnuiiiple processor mid vector processing organizations.

The book also includes an extensive glossary. a list of frequentiv used acronyms, and a bibliography. Each chapter includes homework problems, review questions, a list of key words, suggestions for further reading, and recommended Web sites.

A more detailed, chapter-by-chapter summary of each part appears at the beginning of lhaL part,

#### INTENDED AUDIENCE

The hook is intended for both an academic and a professional audience. As a textbook, it is intended as a one- or two-semester undergraduate course for computer science, computer engineering, and electrical engineering majors. It covers all the topic-5 in *CS 220 Computer .0 00f:titre, which* is one of the core. subject areas in the *EE ErA CM Crimputer Cr ricrila 2001 PTFOG*

For the professional interested in this field, the hook serves as a basic reference volume and is suitable for self-study.

#### INTERNET SERVICES FOR INSTRUCTORS AND STUDENTS

There is a Web site for this book that provides support for students and insiruetors. i he wile includes **links to** other relevant sites, copies of the figures and tables from the book in Pflb (Adobe Acrobat) format, and sign-up information for the book's Internet mailing list. The Web page is 11 WilliamS1allings,eonIICO Me.h1rnl: see the section, <sup>-</sup>Web Site for Computer 'Organizationi and Architecture, Sixth Edition'', preceding [his Preface, for more information. An Internet mailing list has been set up so that instructors using this book can exchange information, suggestions, and questions with each other and with the author. As soon as typos or olher errors are discovered. an errata list for this book will be available at <u>hiamStallings.com</u>. In addition, the Computer Science Student Resource site, at

WiiliamStallings,corn/StudentSupport.htud, provides dociimun is, information, and useful links for computer science students and professiona]s.

## PROJECTS FOR TEACHING COMPUTER ORGANIZATION AND ARCHITECTURE

For army instructors, an important component of a computer organization and architecture course is a project or set of projects by which the student gets handson experience to reinforce concepts from the text. This book provides an unparalleled degree of support for including a projects component in the course- The instructor's marmil not **only** includes guidance on how to assign and structure the projects, but also includes a set of suggested projects that covers a broad range of topics from the text:

- Research projects; The manual includes ri series of assignments that instruct the student to research a particular topic on the Web or in the literature, 4md write a report.

- **Simulation projects:** The manual provides support for the use of the two simulation packages: SimpleScalar can be used to explore computer organization and architecture design issues. SkIPCache provides a powerful educational tool for examining cache design issues for symmetric multiprocessors.

- **Readiogireport assignotents: The** manual includes a list of papers in the literature. one or more for each chapter, that can be assigned for the student to read and then write a **short** report

See Appendix C for details.

#### WHAT'S NEW TN THE SIXTH EDITION

In the three years since the fifth edition of this book was published, the field has seen continued innovations and improvements. In this new edition, I try to capture these changes while maintaining u broad and comprehensive coverage of the entire field. To begin this process of revision, the fifth edition of this book was extensively reviewed by a number of professors **who** reach the ;400. In addition, a number of professionals working in the field reviewed individual chapters. The resell is that, in many plac.i.:27., the narrative has been clarified find tightened, and illustrations have been improved. Also, a number of new "field-tested' problems have been added.

Beyond these refinements to improve pedagogy and user friendliness, there have been substantive changes throughout the book. Roughly the NAUTE chapter organization has been retained, but much of the material has been revised and new material has been added. Some of the most noteworthy changes are the following:

• 1A-64/I11inium architecture: This new architecture includes such important Concepts as predicated execution and speculal ive loading. 7 Ills edition features a chapter-length description and analysis.

- Cache memory : Cache memory is a central element in the design of highperformance processors, and cache **detiign** has become increasingly complex. An entire chapter is devoted to this issue in the new edition.

- Optical memory: 'the material on optical memory has been expanded and updated.

- Advanced IMAM architecture: More material has been added to cover this topic, including an updated discussion of SDRAM and RDRAM.

- SMPK, clusters. and NUMA systems: The chapter on parallel organization has been expanded and updated.

- **Expanded instructor support:** As mentioned previously, the book **now** provides extensive support for projects. Support provided by the book Web site has also been expanded,

#### ACKNOWLEDGMENTS

This new edition has benefited from review by a number ill people, **who** gave gen erously of their time and expertise. .1.'he following people reviewed all Or a large part of the manuscript: Willis King (University of I louston), Albert Heaney (California State University), A. S. Pandya (Florida Atlantic University). Yaser Khalifa (University of North Dakota), and Sanjecv Baskiyar (Auburn University).

Thanks also to the many people who provided detailed technical reviews of a single chapter: Nicole Kaiyan, Terje Mathisen, Daniel M. Pressel, Jeff Deifik, Bill Todd. Charlie Cassidy, Andy Isaacson, Alex Potemkin, Michael Spratte. Hatem Yassine. Grzegorz Mazur, Alan. Leholsky. Jonathan Hall. Sophie Wilson, Alan Alexander, David Vickers. Pete. Smoot, and Erik Seligman.

Professor Cindy Norris of Appalachian State University contributed some homework problems.

Professor Miguel Angel Vega Rodriguez, Prof, Dr. Juan Manuel SArichez P6re.e., and Prof. Dr. Juan Antonio Gomez Pulido, all of University of Extremadura, Spain prepared the SMPCache problems **in** the instructors manual and authored the SMPCache User's Guide.

Bezenek of the University of Wisconsin and Janes Stine of Lehigh University prepared I he SimpleScalar problems in the instructors manual, and Todd also authored the SimpleScalar User's Guide.

## ABOUT THE AUTHOR

WI L..1..J.ANI ST.ALLINGS has made a unique contribution to understanding the broad sweep of Icchnictil developments in computer networking and computer architecture. I.ic has E3tithored 1.7 tiller, **Lin.d.eounting** revised edilions, a total of .35 books on various .:]ir pecits. ol' these subjc.ets..1-'or live vt.7,an, **ill ET row.**. he has; been the•recipient of the award for the hest Computer Science and Prigineering t.c:01),..),..pk of the year from the Textbook **kind** Academic Authors Association.

In over 2 years in the field. Dr. Stallings lias heel' a technical contrib-Lltor,.. technical **manager** and an executive. with several high-technology firms. He is an independcill cor.isuhant whose clients have included computer **Ind** networking rrizmufacturers and custorners.. s.oftm...;ii.c devel opmetit firm..., and leading.4.2dge government research institutions, He: created and maintains the Computer Sciefice Student 1-Z. the several se

iIILam St. a I tin gs.eorniS I 0 de n i S u pport .131m.l.

=:-?f, ... 81514 'i 'e filmfi I Sl 25 BO.1.\*.A. 3.7.785. -WI-X 1 FF M -!• -;+:-.1.1c.-\*\* :0-1: ...., <sup>x</sup>i:it.; <sup>1</sup>**1Ai**43,14**O**: <sup>1</sup>4.5.ilff P<sup>2.1</sup> 2**X**<sup>2</sup> ec!Fil.1....41.r \_e::!;? lr" ...Ar.fr.r-tt if: "-,"()4"".... e.5.:4.6::Dr..1.4.-ril X:VOr .. Pt.t.4:4.1 ....1; SA.,...11,, € 4763 S 1 2 € C 1 1 12 1 aZ % Ari... ..5...\*E.5..s;;....0.:;;=',1\$1;';gr...?5essLIEF.:,,":::,4-;.:-:i; .X0 \*·)srfi ::§1:9;;**W**1 x "% 11. s -ee " fi S f + f

## Overview

PART

ONE

#### ISSUES FOR PART ONE

The purpose of Part One is to provide a background and context for the remainder of this book, The fundamental concepts of computer organization and architecture are presented.

#### **Chapter 1 Introduction**

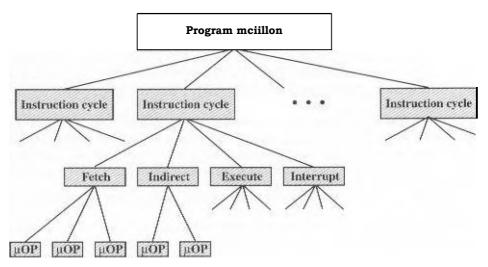

Chapter I introduces the concept of the computer as a hierarchical system. A computer can be viewed as a structure of components and its function described in terms of the collective function of its cooperating components. **Cach** componeni, in turn, can be described in terms of its internal structure and function. The major levels of this hierarchical view arc introduced. The remainder of the. book is organized, top down, using these levels,

#### **Chapter 2 Computer Evolution and Performance**

Chapter 2. serves two purposes. First, a discussion of the history of computer technology is an easy and interesting way of being introduced to the basic concepts of computer organization and architecture. The chapter also addresses the technology trends that have made performance the focus of computer system design and previews the various techniques and strategies that are used to achieve balanced, efficient performance.

## **CHAPTER**

## INTRODUCTION

1.1 Organization and Ambitii.eture

1.2 Structure and Function

Function .StructuDe

1.3 Why Study Computer Organization and Architecture?

1.4 Outline AeBook

1.5 Internet and VVreb Resources

Web Sites rot This Book Other Web Sites US EN F.:f Newsgroups **T** hi, hook is about the structure and function of computers. Its purpose is to present, as clearly and completely as possible, the nature and characteristics (A modern-day computers. This task is a challenging one for two reasons. I.irst, there is a tremendous variety of products, from single-chip microcomputers costing a few dollars to supercomputers costing tens of millions of dollars, Ihat can rightly claim the name *computer*. Variety is exhibited not only in cost, but also in size, performance, and application. Second. the rapid pace of change that has always characterized computer technology continues with no letup. These changes cover all aspects of computer technology, from the underlying integrated circuit technology used to construct computer components to the increasing use of parallel organization concepts in combining those components.

In spite of the variety and pace of change in the computer field. certain fundamental concepts apply consistently throughout. To be sure, the application of these concepts depends on the current stale of technology and the priceiperformance objectives of the designer. The intent of this book is to provide a thorough discussion of the fundamentals of computer organization and architecture and to relate these to contemporary computer design issues. This chapter introduces the descriptive approach to be taken and provides an overview of the remainder of the book.

#### **1.1 ORGANIZATION AND ARCI11TliCTURE**

In describing computers, a distinction is often made between *computer archieecture* and *computer organizinion*. Although it is difficult to give precise definitions for these terms. a consensus exists about the genera] areas covered by each (e.g., see [VRANNOI. [SIEW82], and IBELL78a]).

Computer architecture refers to those attributes of a system visible to a programmer or, put another way those attributes that have a direct impact on the logical execution of a program. Computer organization refers to the operational units and their interconnections that realize the architectural specifications. Examples of architectural attributes include the instruction set, the number of bits used to represent various data types (e.g., numbers, characters), I/O mechanisms, and techniques for addressing memory. Organizational attributes include those hardware details transparent **to** the programmer, such as control signals, interfaces between the computer and peripherals, and the memory technology used.

As an example. it is an architectural design issue whether a computer will have a multiply instruction. It is an organizational issue. whether that instruction will be implemented by a special multiply unit or by a mechanism that makes repeated use of the add unit of the system. The organizational decision may be based on the anticipated frequency of use of the multiply instruction, the relative speed of the two approaches, and the cost and physical size of a special multiply unit,

Historically, and still today, the distinction between architecture. and organization has been an important one, Many computer manufacturers offer a family of computer models, all with the same architecture but with differences in organization. Consequently, the different models in the family have different. price and performance characteristics. Furthermore, a particular architecture may span many years and encompass a number of different computer models. its organization changing with changing technology. A prominent example of both these phenomena is the IBM System/370 architecture. This architecture first introduced in 1970 and included a number of models. The customer with modest requirements could buy a cheaper, slower model and, if demand increased, later upgrade to a more expensive. faster model without having to abandon software that had already been developed. Over the years, IBM has introduced many new models with improved technology to replace older models, offering the customer greater speed, lower cost, or both. These newer models retained the same architecture so that the customers software investment was protected. Remarkably. the Systemi370 architecture, with a few enhancements. has survived to this day as the architecture of IBM's mainframe product line.

In a class of computers called microcomputers, the relationship between architecture and organization is very close. Changes in technology not only influence organization but also result in the introduction of more powerful and more complex architectures. Generally, there is less of a requirement for generation-to-generation compatibility for these smaller machines. Thus, there is more interplay between organizational and architectural design decisions. An intriguing example of this is the reduced instruction set computer (RISO, which we examine in Chapter 12.

This book examines both computer organization and computer architecture\_ The emphasis is perhaps more on the: side of organization. I lowever, because a computer organization must be designed to implement a particular architectural specification, a thorough treatment of organization requires a detailed examination of architecture as well

#### **1.2 STRUCTURE AND FUNCTION**

A computer is a complex system; contemporary computers contain millions of elementary electronic components. How, then. can one clearly describe them? The key is to recognize the hierarchical nature of most complex systems, including the computer [SIM069]. A hierarchical system is a set of interrelated subsystems, each of the latter, in turn, hierarchical in structure until we reach some lowest level of elementary subsystem.

The hierarchical nature of complex systems is essential to both their design and their description. The designer need only deal with a particular level of the system at a time. At each level, the system consists of a set of components **and** their interrelationships. The behavior at each level depends only on a simplified, abstracted characterization of the system at the next lower level, Al each level, the designer is concerned with **Structure** and function:

- Structure: The way in which the components are interrelated

- Function: The operation of each individual component as part of the structure

In terms of description. we have two choices: starting at the bottom and building up to a complete description, or beginning with a top view and decomposing the system into its subparts. Evidence from a number of fields suggests that the topdown approach is the clearest and most effective [WEIN75].

#### **6** CI-BYTER 1 INTRODUCTION

The approach taken in this book follows from this viewpoint. The computer system be duscribed from the top down. We begin with the major components of a computeY, describing their structure and function, mid proceed to successively tower laycN of the hierarchy. The remainder of this fection provides a very brief overview of this plan of attack.

#### F unc tion

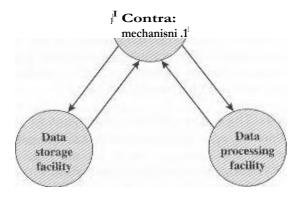

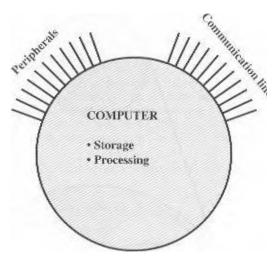

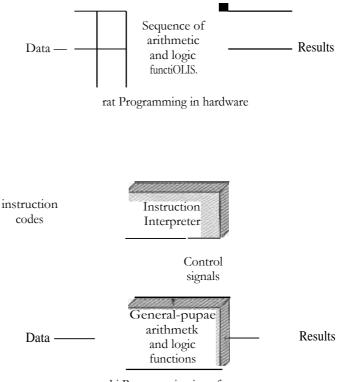

Roth the structure and functioning of a computer are, in essence, simple, Figure 1.1 depicts the basic functions thal a computer can perform. In general term, there are on4' four:

- Data processing

- Data storage

- Data movement

- C0111-rtg

Operating eirviroxinient t'..ourou and destinatiun J datall

Figure Li A Functional Victv of thc. Computer

The computer, of course, must be able to *process data*. The data may take a wide variety of forms, and the range of processing requiretnents is broad. However, we shall see that there are Only a few fundamental methods or types of data processing.

It is also essential that *computer store do* u. Even it' the computer is processing data on the fly data come in and get processed, and the results go out immediately), the computer must temporarily store at least those pieces of data that are being worked on at any given moment. Thus, there is at least a short-term data storage function. Equally important, the computer performs a long-term data storage function. Files of data are stored on the computer for subsequent retrieval and update.

The computer must he able to *move data* between itself and the outside world. The computer's operating environment consists of devices that serve as either sources or destinations of data. When data are received from or delivered to a device that is directly connected to the computer, the process is known *as inpurourPlit (1r'O). and* the device is referred to as *a perfpheral*. When data arc moved over longer distances, to or from a remote device, the process is known as *data commanications,*

Finally, there. must be *control* of these three functions. Ultimately, this control is exercised by the individual(s) who provides the computer with instructions. Within the computer, a control unit manages the computer's resources and orchestrates the performance of its functional parts in response to those instructions.

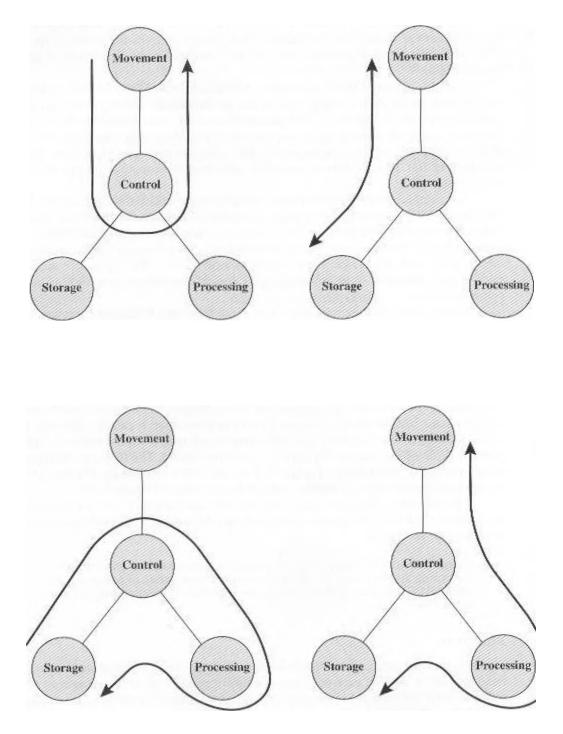

Al this general level of discussion, the number of possible operations that can be performed is few. Figure 1.2 depicts the four possible types of operations. The computer can function as a data movement device t Figure 1.2a), simply transferring data from one peripheral or communications line to another. It can also function as a data storage device (Figure 1.21)), with data transferred from the external environment to computer storage (read) and vice versa (write). The final two diagrams show operations involving data processing, on data either in storage (Figure 1.2e) or en route between storage and the external environment (Figure 1,2d),

The preceding discussion may seem absurdly generalized, it is certainly possible, even at a top level of computer structure, to differentiate a variety of functions, but, to quote 1SIEW821,

There is remarkably little shaping of computer structure to fit the function to be performed. At the root of this lies **the** general-purpose nature of computers, in which all the functional specialization occurs at the time of programming and not at the time of design.

#### Structure

Figure 1.3 is the simplest possible depiction of a computer. The computer interacts in some fashion with its external environment, In general, all of its linkages to the external environment can he classified as peripheral devices or communication lines. We will have something to say about both types of linkages.

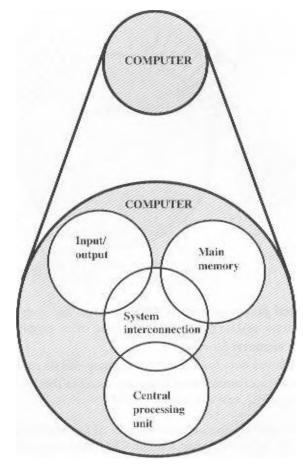

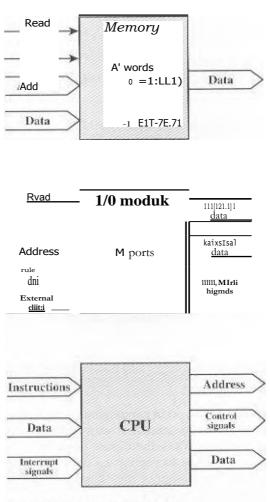

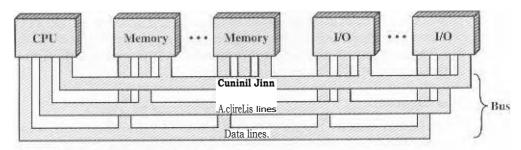

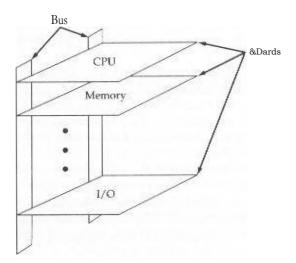

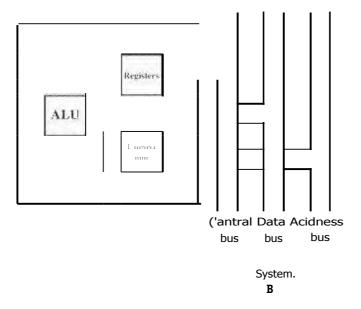

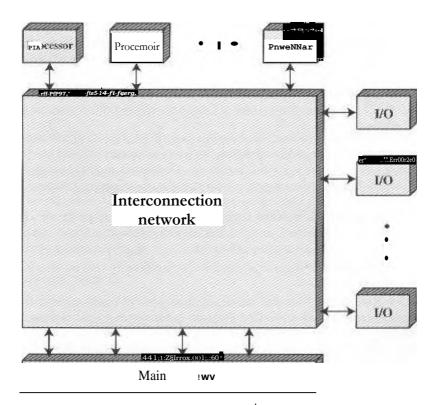

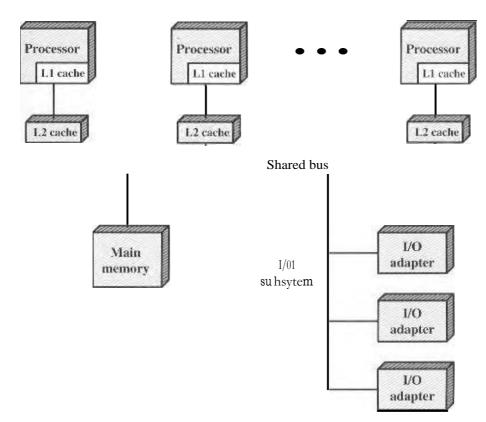

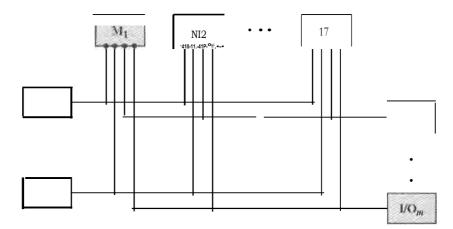

But of greater concern in this book is the internal structure of the computer itself, which is shown at a top level in Figure 1.4, There are four main structural components:

#### 8 CI-TATTER 1 / INTRODUCTION

Figark: 1.3 The Computer

- Central processing unit (CPU): Coma)Is the operation oI the computer and performs iEs drug processing functions often simply referred lo as *procinaer*

- Main memory: Stores data

- 110: Moves daia between the computer and its external environment

- System interconnection]: Some mechanism that provides for communication among CPU, rmin memory, and I/O

There may he one or more of each of the aforementioned components, Traditionally, there has htxn just a Singh: CPI:, In recent years, there has been increasing use of multiple processors in a single computer. Some design issues relating to multiple processors crop up and are discussed as the text proceeds: Part Fire focuses on such computers,

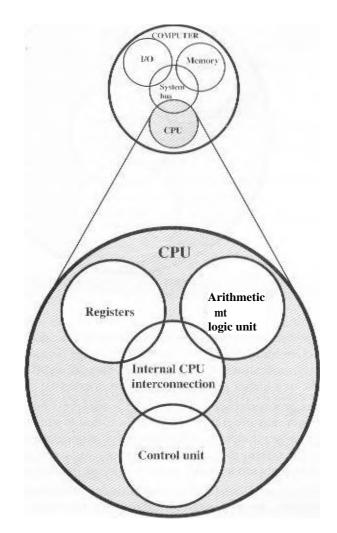

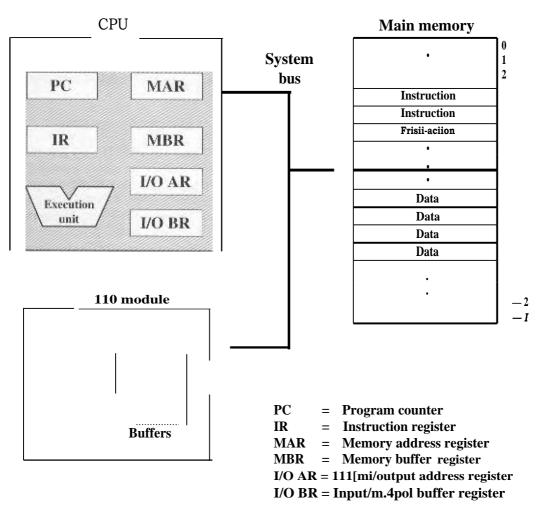

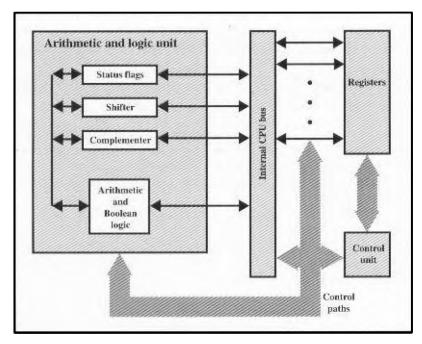

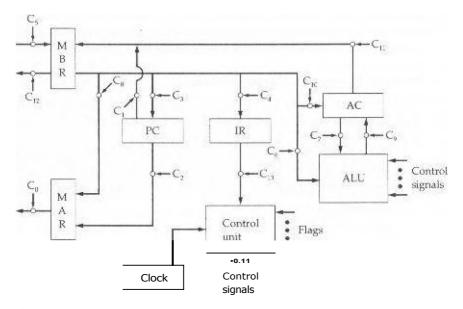

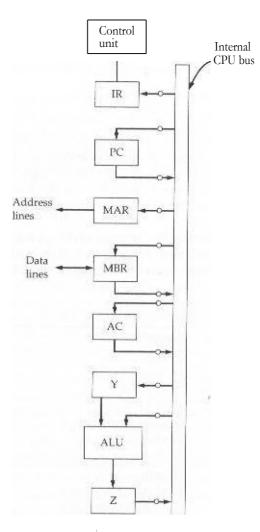

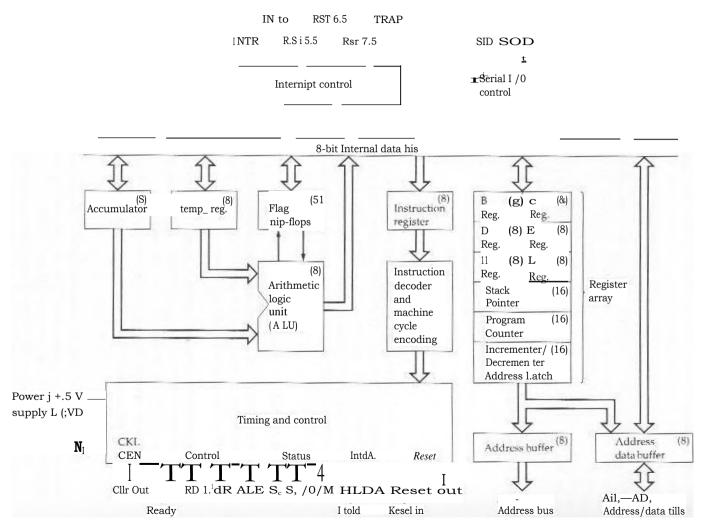

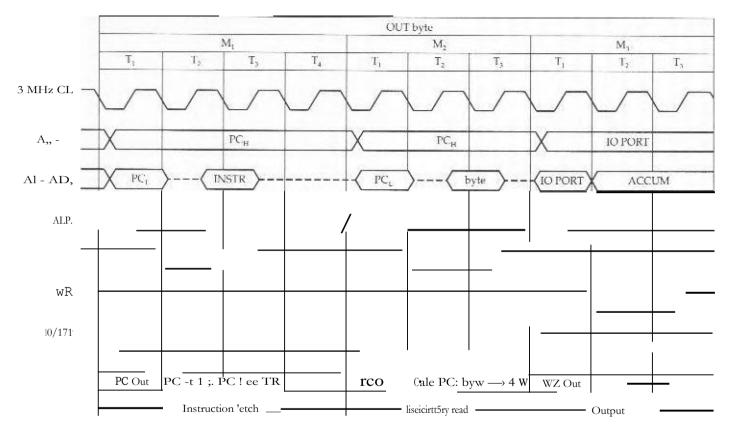

Each of these components will he examined in some detail in Pad Iwo. However, for our purposes, the most interesting and in mile ways the most complex **component** is the  $(:1^3)_{,,,}$  its structure is depicted in Figure 1\_5. Its major structural components are as follows:

- Control unit: Controls the operation of the CPU and hence the computer

- Arithmetic and logic unit (ALU): Performs the computer's data processing functions

- Registers: Provides storage inl erna I to the CPU

- **CPU interconnection:** Some mechanism that provides for communication among the control unit, ALU, and registers

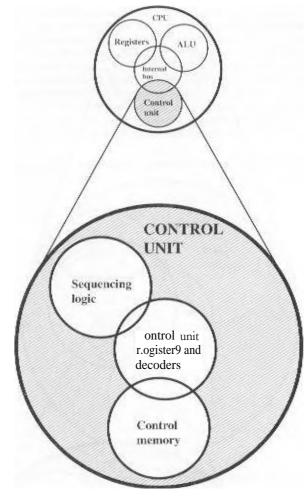

Each Of these components will be examined in some detail in Part Three. where we will see that complexib, y is added by the use of parallel and pipeiined organizational techniques, Finally. 1]iere arc several apprenches to the implementation of the control unit, but the most common is a *microprogrammed* impiernentation• In essence,

Fivre 1.4 The Com1)111cr: rop-Lcvel Structu

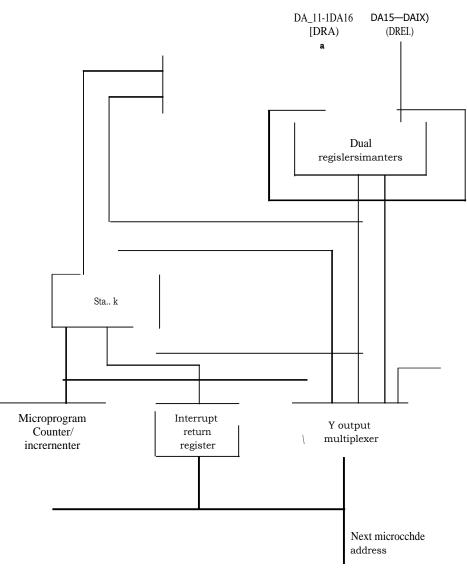

microprogrammed ct **Introl** im t operates by executing microinstructions that tkriElo the functionalily of the control unit, With this approach, the structure of the control unit can be depicted as in Figure 1.6. This structure will be examined in Part Four.

#### 1.3 WHY STUDY COMPUTER ORGANIZATION , AND ARCHITECTURE?

*ThQ1ELESACM Complier Curricula 200] Iii* 1, prepared by the Joint Task Force on Computing Curricula of the IEEH (Institute of Electrical and Electronics Engineers) Computer Society and ACM (Association for Computing Machinery). lists computer architecture ari one of the core subject! i that should be in the curriculum  $\{,f \text{ all students in computer science and computer engineering. The report says the following: } \}$

#### i WHY STUDY COMPUTER ORGANIZATION AND ARCHITECTURE? ii

The. compuiler lies at the heart or compoling. Without it most of the cornputing disciplines today would be a branch of theorotical mathematics. To be a professional in any field of computing today, one sli ould not regard the computo as inst a black box That executes programs by magic. All students of computing should **acq** uire some and erstandin and appreciation of a cc.kmptiter s} stern's functional eumponents, their charact4:risties their perforinanm, and their interactions. There are prnctical implications as well. Students aced tik understand computer iirehitecture irk order trk structure a program so that it runs moire efficiently on a real machine\_ in selecting a system to usu. Ilicy should is able, to Unilurstand the tradeoff aniung various componints, such as CPI! clock speed vs. ir n

ICLEN1001 givG5 the following examples w reasons for studying computer architecture:

Figure 1-5 The Cendr.ill l'ruc.:c.ssing Unit (CPU)

Figure 1.6 Conirol Unit

- Suppose a graduate enters the inclus..lry and is asked to select the namt costeffective computer for use throughout a large organization. An understanding ()I' the implications or spending more for various alternatives. such as a largo' cache or a higher processor clock rare, is essential to making the deciSion.

- 2. Many processors arc not used in PG or servers but in embedded systems, A designer rria:%.' program it processor in C that is embedded in some real-time or larger system, such as 4i11 intelligent automobile electronics. controller. Debugging the system may require the use of a logic analyzer that displays tic..relationship between interrupt requests from engine sensors and machine-level code,

- 3. Concepts used in computer architecture find application in other courses. In particular, the way **in** which the computer provides architect ural support for programming languages and operating system facilities reinforces concepts Front those areas.

As can he seen by perusing the table of contents of this book, computer organization and architecture encompasses a broad range of design issues and concepts. A good overall understanding of these concepts will he useful both in other areas of study and in future work after graduation.

#### **1.4 OUTLINE OF THE BOOK**

The hook is organized into five parts:

- Part One

Provides an overview of computer organization and architecture and looks at how computer design has evolved\_

- **Part Two:** Examines the major components of a computer and their interconnections, both with each other and the outside world. This part also includes a detailed discussion of internal and external memory, and of I/O. Finally, the relationship between a computer's architecture and the operating system running on that architecture is examined.

- **Part Three;** Examines the internal architecture and organization of the processor. This part begins with an extended discussion Of computer arithmetic, Then we look at the instruction set architecture\_ The remainder of the part deals with the structure and function **of** the processor, including a discussion of RISC and superscalar approaches, as well as a detailed look at the IA-64 architecture,

- **Part Four.** Discusses the internal structure of the processor's control unit and the use of microprogramming.

- **Part Five:** Deals with parallel organization, including symmetric multiprocessing and clusters\_

#### **1.3 INTERNEr AND WEB RESOURCES**

There are a number of resources available on the Internet and the Web to support this book and to help one keep up with developments in this field.

#### Web Sites for This Book

A special Web page has been set up for this book at WilliamStallings.comiCOAfie.html. See the two-page layout at the beginning of this hook for a detailed description of that site.

An errata list for this book will be maintained at the Web site and updated as needed. Please e-mail any errors that you spot to me. Errata .sheets for my other books are at WilliamStallings.com.

/ also maintain the Computer Science Student Resource Site. at WilliamStallings.comiStudentSupport,htmh. the purpose of this site is to provide documents, information, and useful links for computer science students and professionals, Links are organized into our categories:

- Math: Includes a basic math refresher, a queuing analysis primer. a number system primer, and links to useful math Web sites

- Flow-tu: Advice and guidance for solving homework problems, writing technical reports. and preparing technical presentations

- Research resources; Links to important collections of papers, technical reports, and bibliographies

- Miscellaneous: A variety of useful documents and links

#### **Other Web Sites**

**There** are numerous Web sites that provide information related la the topics of this book. In subsequent chapters, pointers to specific Web sites can be found in the "Recommended Reading and Web Sites' section. Because the URLs for Web sites tend to change frequently. I have not included these in the book. For all of the Web sites listed in the book, the appropriate link can be found at this book's Web site. Other links will be added when appropriate.

,----- The following are Web sites of general interest related to computer organization and architecture:

- VielleVi Computer Architecture Home Page; A comprehensive index to information relevant to computer architecture researchers, including architecture groups and projects, technical organizations, literature, employment, and commercial information

- **CPU Info Center:** Information on specific processors, including technical papers. product information, and latest announcements

- ACM Special Interest Group on Computer Architecture: Information on SI GA RCH activities and publications

- **IEEE Technical Committee on Computer** Architecture: Copies **of** TCAA newsletter

#### **USENET** Newsgroups

A number of US /NKT newsgroups are devoted to some aspect of computer organif.ation and architecture. As **with** virtually all USENET groups, there is a **high** noise to signal ratio, but it is worth experimenting to see if any meet your needs. The most relevant are as follows:

- comp.arch.: A general newsgroup for discussion of computer arch iie.ctui Often quite good.

- comp.arch.arithmetic: Discusses computer arithmetic algorithms and standards.

- **comp.arch.storuge:** Discussion ranges from products to technology to practical usage issues

- cump.parallel: Discusses parallel computers and applications.

## **CHAPTER**

## COMPUTER EVOLUTION AND PERFORMANCE

#### 2.1 A Brief History of Computers

The First Generation: Vacuum Tubes The Second Generation: Transistors The Third Generation: Integrated Circuits Later Generations

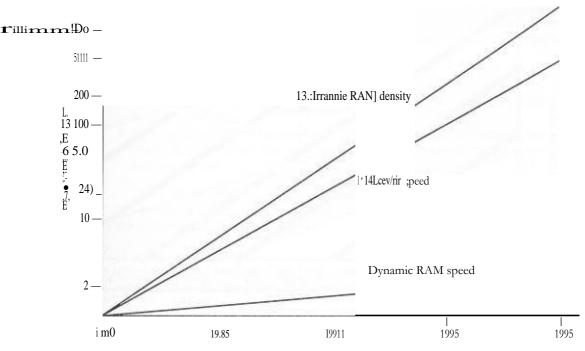

#### 2.2 Designing for Performance

MR ropro ce ssor Speed Performance Balance

#### 2.3 Pentium and PowerPC Evolution

PertEium **Powc: r**

#### 2.4 Recommended Reading and Web Sites

#### 2\$ Key Terms, Review Questions, and Problems

Key Terms Review Questions Pi Phiems,

#### **KEY POINTS.**

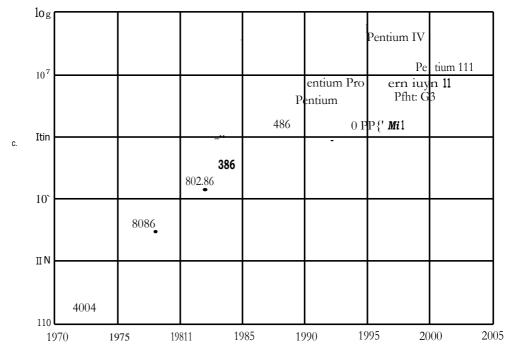

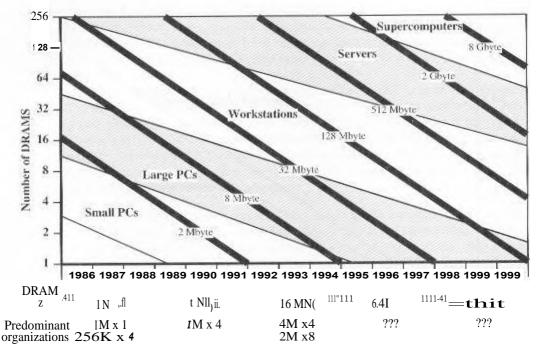

- The evolution of computers has been characterized by increasing processor speed, decreasing component size, increasin2.memory size, and increasing capacity and speed.

- One factor responsible for the great increase in proc-c.squi speed is the shrinking size of microprocessor components; this re-duces the distance between components and hence increases speed. However, the true gains in speed in recent years have come from the organization of the processor, including heavy use of pipelining and parallel execution techniques and the use of speculative execution techniques, which results in the tentative execution of future instructions that ruight he needed. All of these techniques arc designed to keep the processor busy as much of the time as possible.

- A critical issue. in Computer system design is balancing the performance of the various elements. so that gains in pernIrmance in one area arc not handicapped by a lag in other areas, In particular, processor speed has increased more rapidly than memory access time. A variety of techniques is used to compensate for this mismatch, including caches. wider data paths from memory to processor, zind more intelligent memory chips.

c begin our study of computers with a brief history. This history is itself Interesting and also serves the purpose of providing an overview of computer structure and function. Next, we address the issue of performance, A consideration of the need for balanced utilization or computer resources provides a context that is useful throughout the hook. Finally, we look briefly at the evolution of the two systems that serve as key examples throughout the book: Pentium and Power PC,

#### **2.1 A BRIEF HISTORY OF COMPUTERS**

#### The First Generation: Vacuum Tubes

#### **ENIAC**

The ENIAC (Electronic Numerical Integrator And Computer), designed by and constructed under the supervision of John Mauchly and John Presper Eckert at the University Of Pennsylvania, was the world's first general-purpose electronic digital computer.

The project was a response to U.S. wartime needs during World War 11. The Army's Ballistics Research Laboratory (BRL), an agency responsible for developing range and trajectory tables for new weapons, was having difficulty supplying these tables accurately and within a reasonable time frame. Without these firing tables, the new weapons and artillery were useless to gunners. The [IL employed more than 200 people who, using desktop calculators, solved the necessary ballistics equations. Preparation of the tables for a single weapon would take one person many hours, even days.

Mauch a professor of electrical engineering at the[!niversity of Pennsylvania, and Eckert, one of his graduate students, proposed to build a general-purpose computer using vacuum tubes for the 13111..'s application. In 1943, the Army accepted this proposal, and work began on the ENIAC, The resulting machine was enormous, weighing 30 tons, occupying 1500 square feet of floor space, and containing more than 18.000 vacuum tubes\_ When operating, it consumed 140 kilowatts of power. It was also substantially faster than any electromechanical computer, being capable of 5000 additions per second.

The ENIAC was a decimal rather than a binary machine. That is. numbers were represented in decimal form and arithmetic was performed in the decimal system. Its memory consisted or 20 "accumulators.<sup>-</sup> each capable of holding a 10-digit decimal number. A ring of 10 vacuum tubes represented each digit. At any time, only one vacuum tube was in the ON slate, representing one of the 10 digiEs. The major drawback of the ENIAC was that it had to he programmed manually by setting switches and plugging and unplugging cables.

The ENIAC was completed in 1946, too late to he used in the war effort, Instead. its first task was to perform a series of complex calculations that were used to help determine the feasibility of the hydrogen bomb. The use of the ENIAC for a purpose other than that for which it was built demonstrated its general-purpose nature. The EN1AC continued to operate under BRL management until I 955, when it was disassembled.

#### The von Neumann Malithium

The task of entering and altering programs fur the EN IAC was extremely tedious. The programming process could be facilitated if the program could be represented in a form suitable for storing in memory alongside the data Then. a computer could get its instructions by reading them from memory, and a program could be set or altered by setting the values of a portion of memory.

This idea, known as the *wored\_prognan concept, is* usually attributed to the ENIAC designers. most notably the mathematician John von Neumann, who was a consultant on the ENIAC project, Alan Turing developed the idea at about the same time, The first publication of the idea was in a 1945 proposal by von Neumann for a new computer, the EDVAC (Electronic Discrete Variable Computer).

In 1946. von Neumann and his colleagues began the design of a new storedprogram computer, referred to as the IAS computer, at the Princeton Institute for Advanced Studies. The 1.AS computer. although not completed until 1952. is the prototype of all subsequent general-purpose computers.

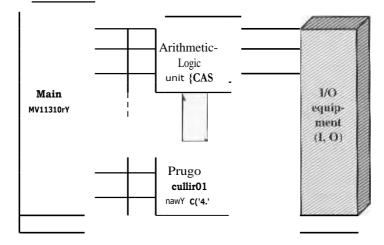

Figure 2.1 shows the general structure of the IAS computer. It consists of the following:

- A main memor!,/, which stores both data and instructions

- An arithmetic and logic unit (ALU) capable of operating on binary data

- A control unit, which interprets the instructions in memory and causes them to be executed

- Input and output (110) equipment operated by the control unit

<u>Central processing unit</u> (CP1;)

Figure 2.1 Structure of the I.XS Computer

This structure was outlined in von Ncurnann's earlier proposal, 'which k Worth quotiny at this point IVONN431..

2.2 First Because the device is primarily a computer, it will have to perform the elementary operations of arithmetic most frequently. These arc addition. subtraction, multiplication and divisioi . it is therefore reasonable that it should contain specialized organs for 061 these operations,

It must 1<sup>+/-</sup> o1.1..R.rved, however, that while this principle as such is probably sound, the specific woy in which it is realized requires close scrutiny. , . At an rate a 4:cierl'al arithmetic:el part of 4111: & vice will probably have to exist .and this constitutes the first vecific pan: (.rl-

2.3 Second: The logical control of the device. that is, the proper sequencing of its operations. can he most efficiently carried out by a central control organ. if the device is to be *elastic*, that is. as nearly as possible *eel.? peapose*, then a distinction must he made between the specific instructions given for and defining a particular T probtem, and the genefal control organs which see to it that these instructions—no matter what they are—are carried out. Tilt Cornier insul he stored in some way., the latter arc represented by definite operating parts of the device, Ft the *cemtral control we* mean this latter function and the organs which perform it form the *second specific part: CC*.

2.4 'Third: Any due ice which is to carry out long and complicated sequences of operations (specifically of calculations) must have a con iderahlc memory .

(11) The instructions which govern a complicated problem may constitute considerable material- particularly so, if the code is circumstantial (which it is in most arrarigement9, This inaledal must he remembered

At any rate, the total memory constitutes the third .specifiC pan of the device: M.

2,6111.4..three specific part **s CA**. **CC** (together (), and **NI correspond** to the *fr.v.so*ciative neurons in the human nervous system. It remains to discuss the equivalents of the sensory or afferent and the. ?no.ror or elfr.rent networs. These arc the *input* and *ow*. pea organs rrf the device ... The device must be endowed with the al a v 10 maintain input and output (sensory and motor) contact with some specific medium of this type. The medium will he called the *outsides mytreling median of the* dm is o:

2.7 Fourth: The device must have organs to transfer ... information from R. into its specific parts C and M. These organs form its *input*, the *Pro.rth specific part: L It* will be seen that it is best to make all transfers from R (.ht into M and never directly from C

2,8 Fifth: The device **must have** organs to transfer ream its specific parts (.• and M into R. These organs form its *ortipar, the fifth specific part.: O. It* will In. seta, that it is again hest to make all transfers from M (by 0) into R. and never directly from C.

With rare exceptions, all of today's computers have this same general structure and function and are thus referred to as von Neumann machines. Thus, it is worthwhile at this point to describe briefly the operation of the !AS computer [BCRIc-Itii. Following [HAYE.98I\_ the terminology and notation of von Neumann arc changed in the following to conform more closely lo modern usage the examples and illustrations accompanying this discussion are based on that latter text.

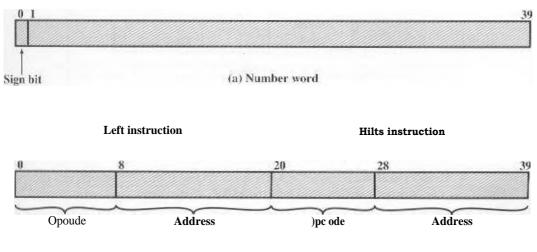

The mem ory of the IAS consists of 11 UU.1 storage locations, called twrds, of 40 binary digits (bits) each. Both data and instructions are stored there. Hence, numbers must be represented in binary form, and each instruction also has to be. a binary code. Figure 2.2 illustrates these formats\_ Hach number is represented by a sign hit and a 39-bit value. A word may also contain two 20-Itit instructions, with each instruction consisting of an s-hit operation code (opcode) specifying the operation to he performed and a 12-hit address designating one of the words in memory (numbered from 0 to 949.

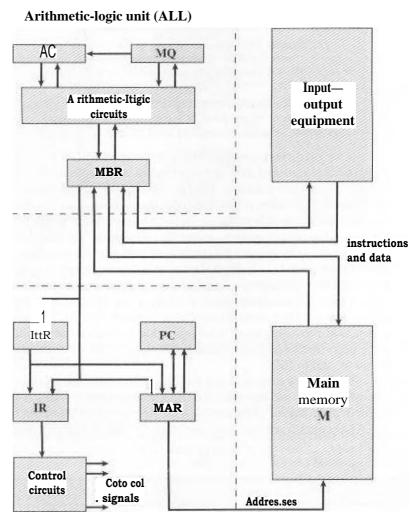

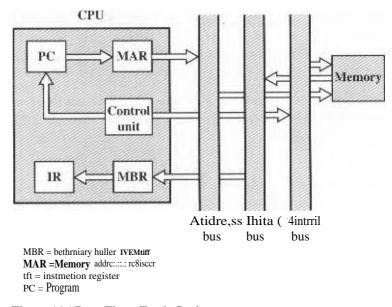

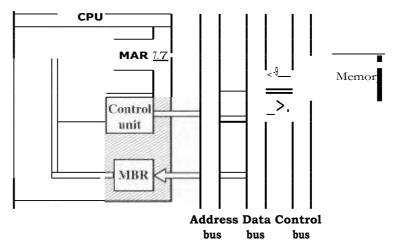

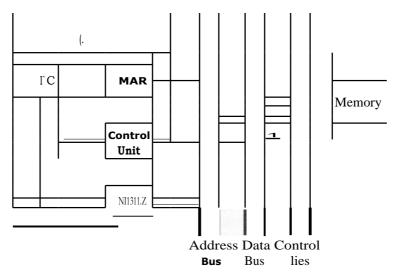

The control unit operates the I AS by fetching instructions from memory and executing them one at a time. Fo explain this. a more detailed structure diagram is needed, as indicated in Figure 2.3. This figure reveals that both the control unit and the ALU contain storage locations, called *registers*, defined as follows:

(b) instruction word

Program control unit (ALL)

Figure 2.3 Expanded Structure of IAS Computer

- **Memory buffer register (MDR): Contains** a word to he. stored in memc.)ry. ar is used to receive a word from memory.

- Memory address register (MAR): Specifies the address in memory of the word to be written from or read into the NIBR.

- Instrudion register (IR): Contains the 8-hit op-code instruction being executed.

- **Instruction buffer register (IBR): Employed acs** hold temporarily the righthand instruction from a word in memory.

- **Program Counter (PC): Contains the** address of the next instruction-pair to be fetched from memory.

Accumulator (AC) and multiplier quotient (MQ): Employed to hold temporarily operands and results of AU! operations. For example, the result of multiplying two 40-hit numbers is an 80-hit number the must significant 40 hits are stored in the AC and the least significant in the MQ.

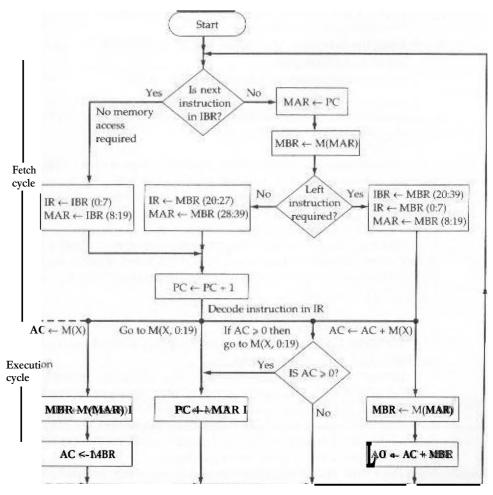

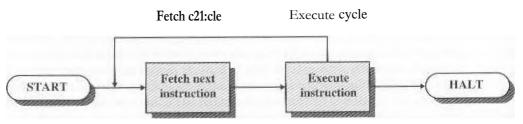

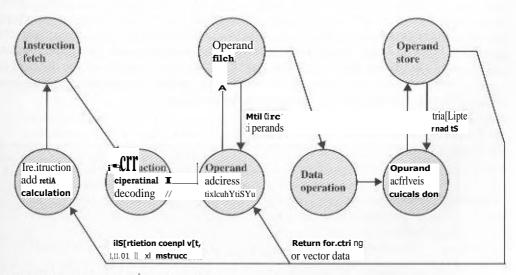

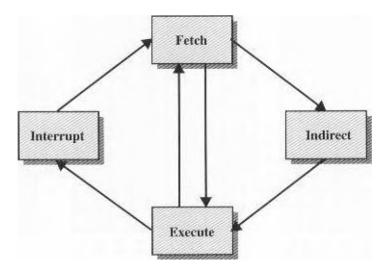

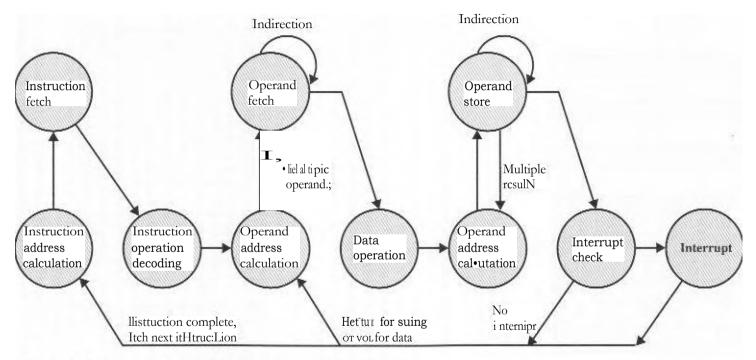

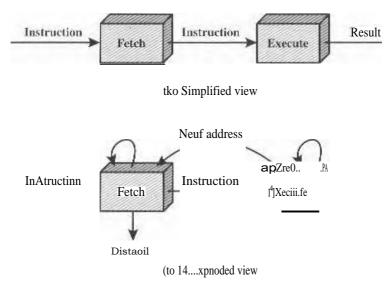

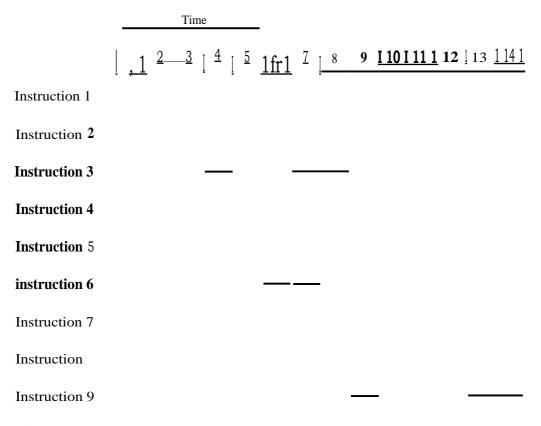

The IAS operates by repetitively performing an *instruction cycle*, as shown in Figure 2.4. Each instruction *cycle* conskis of two subcycles. During. the *fetch cycic*, the opcode of the next instruction is loaded into the IR and the address portion is loaded into the. MAR. This instruction may be taken **from** the **1BR**, or it can be **obtained from memory by** loading 41 word into the MDR. and then down to the 1BR, 1R, and MAR.

M(X) = contents of memory location whose address is X (X) = bits X through

Figure 2.4 Partial Flowchart of IAS Operation

Why the indirection? Those operations are controlled by electronic circuitry and result in the use of data paths. To simplify the electronics, there is only one register that is used to specify the address in memory for a read or write, and only one register to be used for the source or destination\_

Once the opcode is in the IR, the *ex•cure cycle* is performed\_Control circuitry interprets the opcode and executes the instruction by sending out the appropriate control signals to cause data to be moved or an operation to be performed by the ALU.

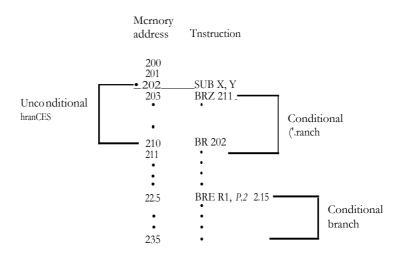

The lAS computer had a total of 21 instructions, which are listed in Table 2.1. These can be grouped as follows:

- Data transfer: Move data between memory and ALL1 registers or between Iwo ALE: registers.

- Unconditional branch: Normally, the control unit executes instructions in sequence from memory. This sequence can be changed by a branch instruction. This facilitates repetitive operations.

- **Conditional branch: 'Fhe** branch can be made dependent on a condition. thus allowing decision points.

- Arithmetic: Operations performed by the ALU.

- Address modify: Permits addresses to be computed in the ALL' and then inserted into instructions stored in memory. 'F'his allows a program considerable addressing flexibility.

Table 2,1 presents instructions in a symbolic, easy-to-read form. Actually, each instruction must conform to the format of Figure 2.2b. The opcode portion (first 8 bits) specifies which of the 21 instructions is Lo he executed. The address portion (remaining 12 bits) specifies which of the 11M141 **memory** locations is **to** be involved in the. execution of the instruction.

Figure 2.4 shows several examples of instruction execution **by the control** unit. Note that each operation requires several steps. Some or these. arc quite elaborate. The multiplication operation requires 39 suboperations, one for each **bit position except** that of the sign bit!

#### **Commercial Cons puters**

The 1950s saw the birth of the computer industry with two companies, Sperry and IBM, dominating the marketplace.

In 1947. Eckert and Mauchly formed the **Eckert-Mauchly Computer** Corporation to manufacture computers commercially. Their first successful machine **was** the UNIVAC I (Universal Automatic Computer), which was commissioned by the Bureau of the Census for **the 1.950 calculations. The Eckert-Mauchly Computer Corporation** became part of the UNIVAC division of Sperry-Rand Corporation, which went on to build a series of successor machines.

'Die UNIVAC I was the first successful commercial computer. It was intended as the name implies, for both scientific **and** commercial applications. The **first paper describing** the system listed matrix algebraic computations. statistical problems, premium billings for a life insurance company, and logistical problems as **a sample of the tasks it could** perform.

| Instruction                    |                    | Symbolic                                        |                                                                                                                 |

|--------------------------------|--------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| <sup>7</sup> /1 <sup>1</sup> e | Opcode             | Representation                                  | Description                                                                                                     |

| DErta transfer                 | 00001010           | LOAD VIO                                        | fra usfer contents register MO to the accumulator AC                                                            |

|                                | 04001001           | LOAD MO.M X)                                    | l'ratisler contents of <i>fneMOky</i> lot:11'60<br>X CO <b>MO</b>                                               |

|                                | <b>001</b> 4111)t1 | STDR MIX                                        | libra:lifer mill En LS IIi elixir Llluk tor CO<br>Tn.:mew!: lomitjon X                                          |

|                                | I MINK11:01        | LOAD KT(X)                                      | Tranhcr r'.1{ X) 1451 ho zieetirmi1m1or                                                                         |

|                                | 1:00:1(11.)10      | LOAD M(X)                                       | Transfer - M(X Li} LhL accurnLIIntor                                                                            |

|                                | IKAXIOI/11         | LOAD NUN)!                                      | TTaa}1C1 4.:111AC" 01 WM to<br>the au:LnntilE11.(ir                                                             |

|                                | CIODOO t Of)       | LOAD   M(X)1                                    | Tionsfer —I47(X) to the :iccumulatu                                                                             |

| Unconditional<br>branch        | (1)]01101          | JL <sup>1</sup> MP MPC,11:191                   | THk ncNI insirlieriOn from left halt <b>c</b><br>KIVX)                                                          |

|                                | 01X100 i 10        | .1 1. <sup>1</sup> 1,I1 <sup>3</sup> M(X.20:39) | Take next irISITUCLICIa         ream rig11         half           !irl(X)                                       |

| Conditional<br>branch          | 1)0001111          | 31:MP+M(X.02191                                 | 11 <b>ninnber m</b> ihc: necumillMor is<br>nOnriuFaiive, inSCuocii on<br>frorn <b>left half</b> 01 <b>MIX</b> , |

|                                | 『)00i0r.i.10       | N•20:119)                                       | <pre>11 r in I hc aLLLI nh nhiI oris<br/>aunn Livc. Lake nix I insl ruction<br/>Cron, righi. half 1.)</pre>     |

| .Arithme tic                   | 00000101           | ADD M(X)                                        | Add M(X1 to A (:; put the remit in A                                                                            |

|                                | 01)001)11          | ADD '11(X)1                                     | Add IM(X)1 10 AC; pi.v he result in                                                                             |

|                                | OfX1(JR1           | 51( }                                           | subtrkirt m(x) rivn, <b>AC</b> ; put the re41.1<br>in AC                                                        |

|                                | (01:)01.01)0'      | Si R IM( X)                                     | SuhLrael. frorEi AC: TruL ih:<br>miniinder 1a AC                                                                |

|                                | 40041(}1 I         | MU]_                                            | Multiply M{X1 by MO: put inosi<br>significant hitE of result in AC. put<br>icant bib., in .M.Q                  |

|                                | (IOW'LOL)          | DJV MIX)                                        | 1)i %dile hy M(X):: put 1.11i rollou<br>in "1();111c1 the ra.maihder iii AC                                     |

|                                | 00411i)(01./       | LSH                                             | <pre>?vjal iply dEcumul Dior I)? <sup>2</sup> 0.0 Shift<br/>!ell. One hil !Imo on1</pre>                        |

|                                | 0001.1111)1        | KSI                                             | Diuide112CU TUIFacIT by 2 fj.C%, stLil<br>rich( one position)                                                   |

| Alkiresr modify'               | 1)0010(110         | STDR trli.X.5:19)                               | Retched Icrl LOdre.5 field at ?41(X:) ht<br>ri eh i-rnoNt hots of AC                                            |

|                                | 000/01)1 I         | <b>STOR</b> M(X,2EI:119)                        | Replace right addrccs i <b>kI</b> 40 M(H) 1<br>[2 right-m(1EL bias arAC                                         |

Table 2.1 the IAS losiruction ScL

The UNIVAC II, which had greater memori, 'capacity and higher TX!rfOrrilaitCC, than the UNIVAC I, was delivered in the laic 1950s and illustrates several trends that have rornainc.d characcetistic of the computer indumry\_\_\_\_\_\_ adviuices in technology allow Companies 1[3 conlnn1.1 to build larger, more powerful computers. Second\_ each company tries to make its new machines upward compatible with the older machines. This means that the programs written for the older machines can be executed on the new machine. This strategy is adopted in the hopes of retaining the customer base: that is, when a customer decides to buy a newer machine, he or she is likely to get it from the same company to avoid losing the investment in programs.

'Ile UNIVAC division also began devclopment of the 1100 series of computers, which was to be its major source of revenue. This series illustrates a distinction that existed at one lime. The first model, the UNIVAC 1103, and its successors for many years were primarily intended for scientific applications, involving long and complex calculations. Other companies concentrated on business applications, which involved processing large amounts of text data. This split has largely disappeared, but it was evident for a number of years.

IBM, which was then the major manufacturer of punched-card processing equipment, delivered its first electronic stored-program computer, the 701, in 1953. The 701 was intended primarily for scientific applications IBAS11811. In 1955, 1BM introduced the companion 702 product, which had a number of hardware features that suited it to business applications. These were the film of a long series of 70017000 computers that established I HM as the overwhelmingly dominant computer manufacturer,

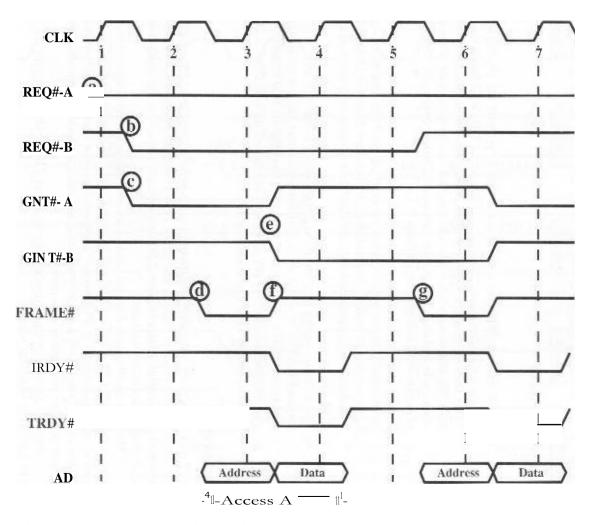

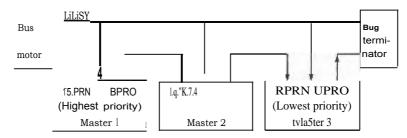

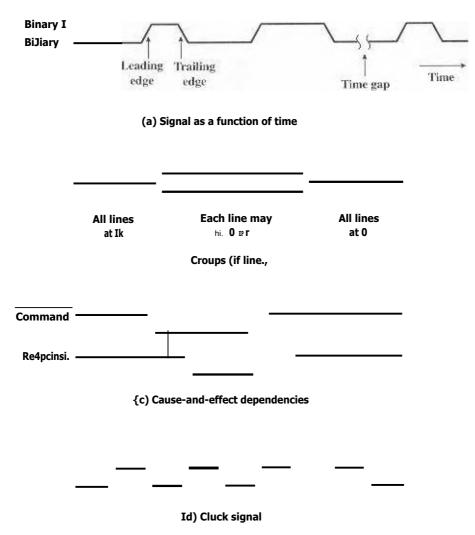

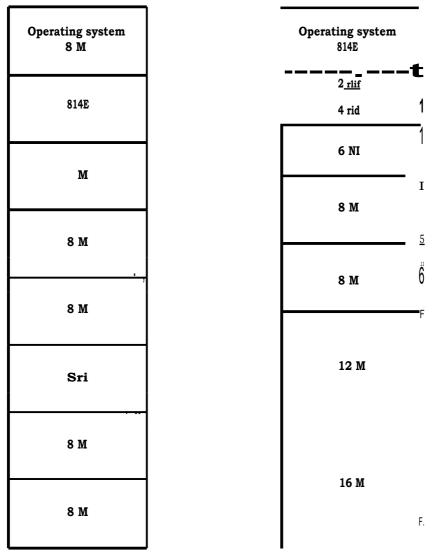

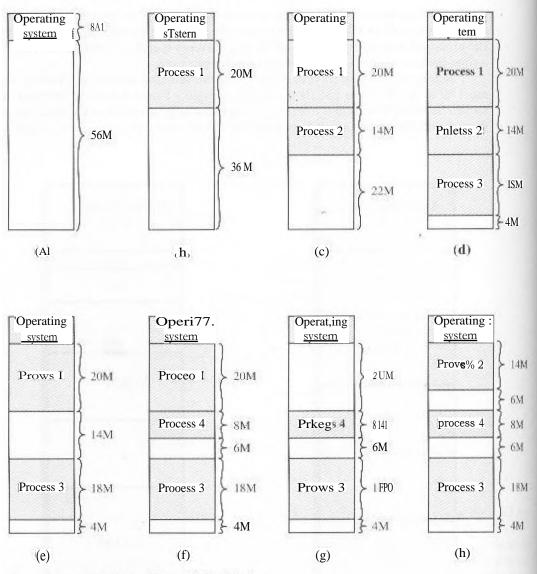

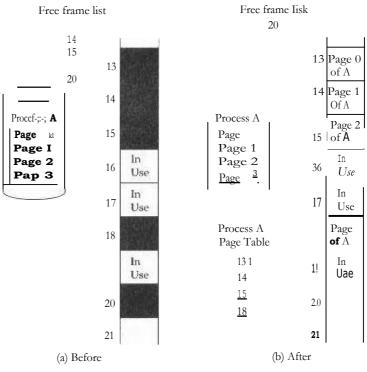

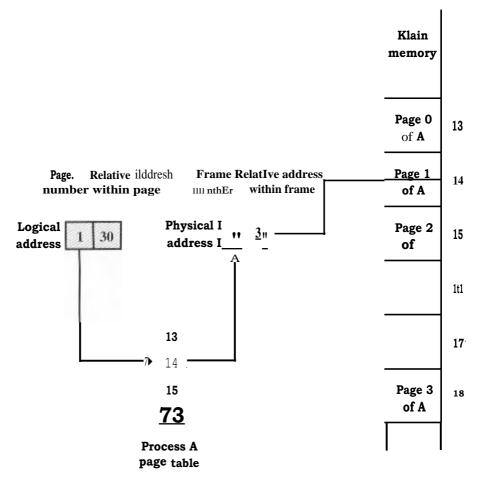

# The Second Generation: Transistors